技术分享

了解最新公司动态及行业资讯

一种小型化软件无线电通信平台设计

摘要:该文针对小型化软件无线电平台轻量化、低功耗设计要求,提出了一种基于SOC芯片的开放性、标准化、小型化的 软件无线电通信平台,可实现通信装备架构统一、波形按需加载。 关键词:小型化;软件无线电;通信

0 引言

软件定义无线电平台是基于通用的硬件平台, 使用可编程的软件方法来满足不同需求的无线电系 统[1]。美国国防部在1997年启动联合战术无线电系统 (JTRS)项目[2],目标是研制基于软件无线电标准体 系架构(SCA)的战术电台,使手持式、背负式、机载 式[3]等电台能够相互兼容,但当时的软件无线电架构 主要面向通用的软件无线电系统,并非专门针对小型 化手持平台,难以适应小型化平台的各种资源约束。 2010年和2012年,美国国防部相继发布SCA Next草案 和SCA v4.0,提出了可裁剪的SCA核心框架的概念, 可通过裁剪框架接口达到小型化的目的,为小型化软 件无线电通信平台提供了很好的解决方案。 目前,我国关于小型化通信平台对软件无线电应 用的研究尚处于起步阶段,大部分设备主要针对单波 形应用场景,采用专用平台或者多平台堆叠方式设 计,导致设备功能弱、型谱多、通用性差,极大地限制 了小型化通信平台互联互通互操作能力。为解决以上 问题,通过对比分析现有软件无线电通信平台特点, 笔者提出一种小型化软件无线电通信平台设计思路, 可用于构建开放性、标准化、小型化的软件无线电硬 件平台。

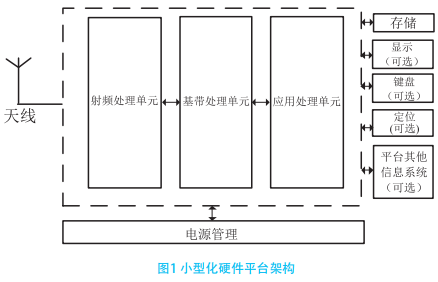

1 小型化硬件平台设计 小型化通信平台一般由天线、射频处理单元、基带处理单元、应用处理单元、电源管理及其他配套外 设组成(如图1所示)。为实现更高的集成度和更低功 耗,小型化通信平台除天线外,各个功能单元往往采 用芯片化的设计思路,有时各功能单元也会集成至一 颗芯片来实现。针对软件无线电架构要求,下面重点对 射频处理单元和基带处理单元进行分析。

1.1 基带处理单元 通信平台基带处理主要由具备可编程能力的通用 处理器(GPP)、数字信号处理器(DSP)和现场可编 程门阵列(FPGA)等实现。根据具体采用的处理器实 现方式,基带平台架构主要分为两大类,一类是采用 多个GPP、DSP和FPGA处理器来完成基带处理功能, 另一类是采用单个包含多个异构处理器核的片上系统 (SoC)芯片来支持基带处理,以下为几种典型基带处 理方案的对比分析:

(1)GPP+DSP+FPGA分立处理方案。基带硬件 平台采用GPP+DSP+FPGA的分立架构,GPP处理器 完成通信波形协议处理及接口扩展等功能,DSP芯片 和FPGA芯片支持波形物理层运行。 (2)GPP+DSP或FPGA分立处理方案。基带硬件 平台选用GPP处理器与DSP芯片或FPGA芯片的分立 架构,GPP处理器完成通信波形协议处理及接口扩展 等功能,DSP芯片或FPGA芯片支持波形物理层运行。

(3)高集成SoC芯片处理方案。基带硬件平台选 用集成GPP/DSP/FPGA的SoC单芯片解决方案,SoC 芯片中GPP处理器核完成通信波形协议处理及接口扩 展等功能,SoC芯片DSP或FPGA核,支持波形物理层 运行。

高集成SoC芯片处理器方案基带将GPP、DSP、 FPGA资源集成在一颗芯片中,与多芯片架构相比,周 边电源芯片PMU、存储器等器件数量最少,设计难度 最低,在功耗、占用面积上也有很大优势,更高速的芯 片内部总线与芯片间总线相比,系统运行的实时性和 稳定性更好,另外随着芯片制程工艺的快速发展,单 芯片处理能力也越来越强。因此针对小型化软件无线 电通信平台基带处理单元,采用高集成SoC芯片处理 方案是最优选择。

目前,应用比较 广泛的高集成 度SoC芯片以 Xilinx公司的ZYNQ系列芯片以及辰芯科技的LC1881 芯片为代表,其中,ZYNQ系列芯片采用集成ARM核 和FPGA核方式实现,而LC1881芯片则采用集成ARM 核和DSP核的方式实现。

ZYNQ系列芯片依托于FPGA,具有较强的波形 运算处理能力,但其仅是单纯地将ARM和FPGA堆 叠,针对小型化软件无线电通信平台而言,在小型化低 功耗方面相较于传统GPP+FPGA方案并不具备较大 的优势。LC1881芯片则采用异构多核的处理方式,基 带处理可由内部集成的矢量DSP核、控制DSP核及多 个硬件加速器等分工处理完成,矢量DSP核负责算法 处理,控制DSP核负责协议主控处理,加速器负责编译 码、FFT这类复杂计算,从而保证高性能的同时有效降 低运行功耗,非常适合小型化软件无线电平台应用。

1.2 射频处理单元

典型的软件无线电射频处理有直接采样和变频采 样两种结构,其中,直接采样是将模拟信号直接在射 频进行采样,从而简化模拟变频电路,使得架构非常 简洁,自组合干扰少,但由于需满足奈奎斯特采样定 理,随着射频频率的提高,这种结构对A/D转换器的性能,如转换速率、工作带宽、动态范围提出了较高的 要求,同时对采样后基带信号处理能力要求也很高;变 频采样结构则是将模拟信号变频到低中频或零中频再 进行采样处理,和直接采样架构相比,高频段可扩展性 好,但存在本振泄露、直流失调、I/Q不平衡等问题。

两种射频结构各有优势,针对小型化通信平台而 言,根据用户使用特点,工作频段一般需覆盖U、V、 L、S频段,特别是在高频段的L、S频段,若使用直接 采样射频结构,则对射频芯片的采样率提出了很高的 要求,按照目前的工艺制造水平,芯片的面积、功耗也 会大大增加,使其很难适应小型化通信平台的应用需 求,因此当前变频采样结构是小型化软件无线电平台 的最优选择。

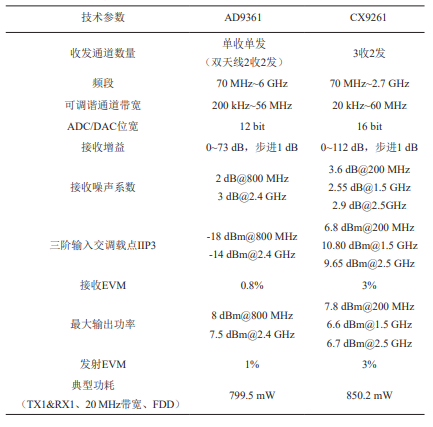

目前,在小型化通信平台应用领域,比较典型的 变频采样结构芯片主要有ADI公司AD9361射频芯片 和国内城芯科技的CX9261综合射频芯片,主要参数对 比如表1所示。

表1 两种典型变频采样射频芯片对比分析

由表1对比可以看出,CX9261接收通道数量比 AD9361多一个,并且各通道配置了不同的频率综合 器,保证了各通道的独立工作,从而更好地支持多通 道并发场景;CX9261支持频段范围比AD9361小,但 CX9261的AD/DA位宽优于AD9361,因而具备更高 的接收动态范围;接收通道噪声系数二者相当,但 CX9261拥有更高的接收增益和IIP3,能够抗更大的带 内及带外信号干扰;最大输出功率二者相当,CX9261 的EVM稍差,典型工作功耗CX9261略高。这两款芯 片最主要的特点是集成度高、功耗小,非常适合小型 化软件无线电通信平台的应用。

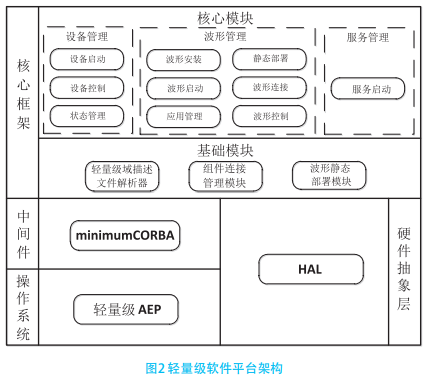

由于小型化软件无线电通信平台对于功耗和体 积的要求非常严格,传统SCA软件平台架构并不适 用,这就需要通过对软件平台中的核心框架、操作 系统、中间件等部分进行裁剪和优化设计,简化软 件平台配置,从而最大程度降低平台软件运行造成的 不必要的系统资源消耗,提高系统启动和波形重构速 度,如图2所示。

2.1 核心框架轻量化设计

核心框架是应用层接口和服务的基本“核心”集, 为波形应用软件设计者提供对底层软件和硬件的高层 次抽象。

(1)跨平台设计。小型化通信平台采用的操作系 统多种多样,核心框架作为运行于操作系统之上的核 心服务软件,必须充分考虑跨平台移植性,否则,将会 带来在不同操作系统间移植核心框架的巨大工作量。 为了保证核心框架软件能够在主流操作系统平台上进 行平滑移植,在核心框架软件设计时,对主流操作系统 平台的POSIX支持性进行了深入分析,对POSIX规范 中的接口进行了裁剪,摈弃了所有与特定平台相关的系 统调用,只使用所有平台都兼容的POSIX接口,核心框 架代码全部采用标准C/C++语言开发,并通过宏定义 来控制不同操作系统平台的编译选项和编译流程。同 时,对于不同平台间的协议差异、编码差异等,核心框 架通过开发封装层进行了屏蔽。通过这些跨平台设计 技术,使得核心框架软件在主流操作系统平台上移植 时,不需要修改任何源代码,只需直接编译即可。

(2)组件及接口设计。考虑到对系统资源和功 耗的严格要求,进一步减少核心框架软件的资源占用,在优化设计时可以裁剪掉核心框架标准中一些 可选组件和不使用的接口,组件如平台组件工厂组 件、应用工厂组件等,接口如ComponentFactory、 ParentDevice、AggregateDevice等。通过轻量化裁剪 降低核心框架的系统管理层次,提高核心框架软件的 执行效率,同时,考虑到与现有系统波形的兼容,基本 应用接口保持不变,不影响波形应用的可移植性。

(3)域配置文件解析优化设计。核心框架软件负 责对所有的域配置文件进行解析,当波形应用比较复 杂、域配置文件比较多时,其解析效率直接影响系统 性能。为此,在核心框架软件开发时,设计了一个高效 的域配置文件解析引擎,对于系统中所有的域配置文 件,只有在第一次使用时才打开进行解析,一旦解析 结束,所有解析结果保留到一棵解析树上,这样,下次 使用该域配置文件时,就不用再进行解析,而只需获取 解析树的对象即可。

(4)波形部署管理。针对小型化软件无线电通信 平台对波形应用部署启动和停止卸载指标的严格要 求,通过裁剪核心框架软件在波形部署和卸载过程中 不必要的条件判断,从而实现静态部署等方法,提高 波形部署和卸载的执行效率。

2.2 轻量化中间件设计

中间件作为软件无线电体系结构中操作环境的必 要部分,起到了实现平台系统中组件、任务之间的互 联、互通和互操作,屏蔽系统异构差别和网络协议差 别,完成透明传输的作用。

(1)共享内存本地通信机制设计。针对小型化软 件无线电平台的中间件采用基于共享内存作为本地组 件间的底层通信协议,从而提高组件间的通信效率,同 时将基于以太网底层通信协议进行裁剪,减少传输机 制对系统资源的占用,提升软件平台的轻量化程度。

(2)性能优化。为满足小型化软件无线电通信平 台实时处理的性能要求和具体硬件环境的适应性要 求,中间件还在以下方面进行优化:一是采用影子内 存机制减少锁和互斥信号量的使用,提高多任务并发 访问内存的效率;并在协议封装和解析时采用零拷贝 机制,减少数据移动和内存消耗,提高系统资源的使 用效率;二是采用多线程连接策略,采用异步传输方 式,减少数据传输的延迟,提高底层的通信效率和节 点的并发处理能力。

2.3 硬件抽象层设计

硬件抽象层由通信函数和接口组件两部分组成, 通信函数提供硬件抽象层消息的路由功能,接口组件提供消息传输功能。CPU和DSP硬件抽象层接口组件 为硬件驱动程序,FPGA硬件抽象层接口组件为硬件 接口实体模块。

(1)非阻塞回调接口优化设计。非阻塞接口被上 层组件调用后立即返回,其执行结果是通过回调程序 来处理。针对小型化平台特点,在回调函数的实现中, 通过采用将回调消息放入消息队列的方式处理,应用 组件在另外的线程中从消息队列取出处理,这样可以 大幅减少回调函数的执行时间,从而优化硬件抽象层 的工作效率。

(2)动态可配置的缓冲管理机制。在互联架构 设计中,参考基于DSP处理器移植SCA的实现架构, 设计多个线程来满足波形组件数据和控制命令传输。 实现时为了响应DSP上多个组件端口的收发请求,为 每个组件端口开设一个单独线程,对于DSP上数据进 行操作时需要设定数据写入和读出的处理机制,保护 数据存储区,以确保系统正常运行。在实现中需使用 信号量对多线程和公共存储区进行管理,为DSP的每 个与互联模块连接的端口开设一个线程,只有线程获 取到对信道和存储区操作的信号量时才能响应端口的 请求。

3 验证与分析

3.1 测试环境搭建

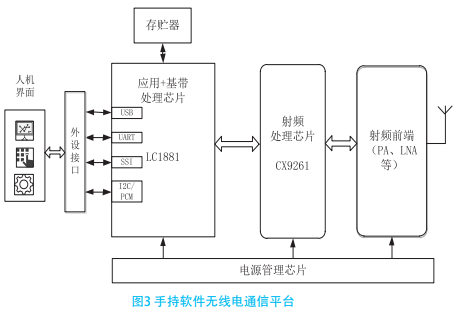

为验证本文设计的小型化软件无线电通信平台 性能,按照图3所示,搭建一种手持软件无线电通信 平台。其中应用和基带处理单元选用高集成SoC芯片 LC1881,射频处理单元选用CX9261综合射频芯片。

3.2 多波形加载验证

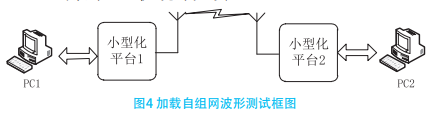

(1)自组网波形加载验证。按图4所示搭建测试 环境,在平台上加载自组网波形,配置波形频率、功 率、速率相关参数,使两个平台通过无线连接组网成功,然后通过PC计算机Iperf软件进行灌包测试。经 10 min测试,PC机统计无丢包。

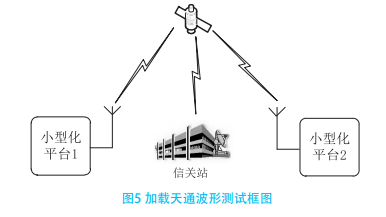

(2)天通卫星波形加载。按图5所示搭建测试环 境,在平台上加载天通卫星通信波形,配置相关参数, 接入天通卫星网络,通过平台1向平台2拨号,接通后保 持10 s,共拨打了10次,均能拨打成功,话音清晰。

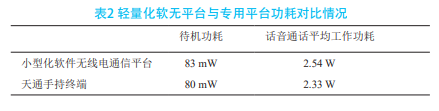

3.3 功耗测试 在平台上加载天通卫星通信波形,接入天通卫星 网络,测试平台待机和话音通话平均工作功耗,与天 通专用手持终端测试对比结果如表2所示。可以看出, 小型化软件无线电通信平台加载天通波形运行功耗与 天通专用平台大体相当。

4 结束语 本文针对目前小型化通信平台型谱多、通用性差 等问题,结合软件无线电与小型化平台的特点,提出了 一种小型化软件无线电通信平台设计思路,介绍了小 型化硬件平台及轻量化软件平台的设计方法,构建了 开放性、标准化、小型化的软件无线电硬件平台。并且 通过搭建的测试环境,对平台多波形加载及低功耗性 能进行了测试,验证了平台设计的基本功能。

王 涛 (中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

参考文献 [1] 陶玉柱,胡建旺,崔佩璋.软件无线电技术综述[J].通信技术,2011, 44(1):37-39. [2] 吴坤兴.美军的联合战术无线电系统(JTRS)[J].舰船电子工程,2022 (3):45-49. [3] 贾哲,吴琼玉,蔡春晓.美军软件定义电台发展研究[J].信息通信, 2018(3):167-168.

上一篇:无人机监测利器:低空监视雷达系统

下一篇:软件无线电的关键技术及应用

售前咨询专员

售前咨询专员