技术分享

了解最新公司动态及行业资讯

基于DDS的快速跳频源设计

引言

跳频通信就是载波频率在较宽频带范围内,伪随机跳变的通信技术。它具有抗干扰性能强、抗截获能力优、抗衰落性能好、通信效果好等优点;同时还能最大限度地利用频谱资源,在军事领域得到了迅速发展。随着无线通信技术的发展,跳频技术以其独特的优势,迅速扩展到民用领域。目前在民用领域的运用包括新一代欧洲GSM 蜂窝状移动通信标准,以及热门的短距离无线通信技术--蓝牙。GSM 蜂窝状移动跳频通信标准在L 频段以 217 Hop/s跳速工作;蓝牙技术采用ISM频段 2.402~2.480GHz,跳速1600 Hop/s,频点数 79个。此外,美国陆、海、空三军共同使用的联合战术信息分发系统JTIDS(joint tactical information distribution system)采用了L波段快速跳频方式,其跳频速率不小于76 923 Hop/s。因此,自主研究新一代高频段、快速、高稳定度跳频信号源,对加快抗干扰、保密通信的发展具有重要意义。为此,我们重点研究L波段、快速捷变、低相位噪声、低杂散特性的跳频频率源。

合成方法和设计指标

目前短波、超短波跳频源的跳频速率都比较低,大都在每秒数百跳到千跳的范围内。随着现代电子技术的迅速发展和新产品不断问世,高处理时钟频率DDS(AD9858处理时钟达1GSPS)及新型PLL的诞生,为我们设计出满足不同要求的高性能指标的跳频源提供了方便。目前高频段频率源的合成方法主要有:

① PLL直接倍频法:可以将高稳定度和精确度的参考频率倍频至上 GHz,合成的频率源稳定度高、杂散抑制度好,但锁定时间较长、频率分辨率较差、跳频范围有限:

②) DDS+PLL 组合法:它又包括 DDS 激励和内插 PLL,两种方法。前一种可是 PLL倍频法的扩展,将参考源改用易控制的 DDS信号源,这样输出频率可以很方便地改变;但是频率源分辨率较低,频率锁定时间较长。内插法是在锁相环的环路滤波环节加入混频器,这样合成的频率源分辨率高,但带宽较窄,锁定时间较长。从简单的分析不难看出,DDS+PLL需要一定频率锁定时间,不适用于快速跳频源:

③ DDS+本振源混频法:是将 DDS 输出的捷变频率源与本振源混频后上变频至需要频段。该方法具有 DDS的很多优点,只要本振源指标足够好,就能够满足快速捷变、低杂散、低相位噪声等多项性能指标。但受限于DDS 的输出带宽,跳频源的带宽不能太宽。

本着尽量节省硬件资源,尽可能地提高频率源的稳定度、杂散等指标的原则,我们采用 DDS 与本振源混频法,来实现L 波段快速捷变跳频源。根据 DDS 理想频谱输出特点,综合考虑各项性能指标因素的相互影响,DDS选用50MHz的跳频带宽:本振源用单频锁相环合成技术,可以提供指标较优的本振源信号。

1.1 设计技术指标

本研究目的是在满足跳频速率的前提下,尽量降低相位噪声、抑制杂散和谐波电平,我们的设计技术指标如下:

① 频段范围:L波段(950~1050 MMHz):

②带宽:100 MHz:

③ 频率切换时间:小于5us;

④)跳频频隙:1MHz;

⑤相位噪声优于:-80dBc/Hz@1kHz,-120dBc/Hz@1 MHz;

6.杂散抑制优于:-50dBc。

2 DDS 频谐分析

2.1 DDS 的理想频谱

DDS 的基本原理可参看相关文献"-2),在此我们重点分析DDS 输出频谱理想 DDS 频谱分析包括三个条件:

①无相位截断误差,即存储2~位值(N为相位累加器位数);

②正弦幅度存储表没有量化误差,即正弦存储表的幅度值用无限长二进制代码表示:

③数模转换器分辨率无穷大,并且具有理想数模转换特性。

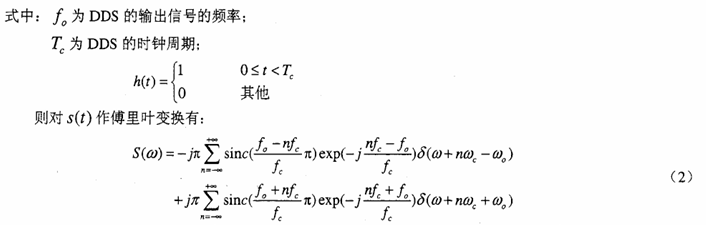

在理想 DDS 模型中,DAC以前可以等效为一个理想采样电路“1~2,则从ROM 输出的阶梯波形序列s(n)的函数可以表示为:

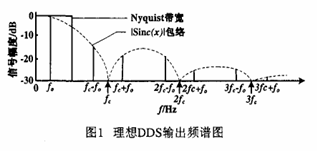

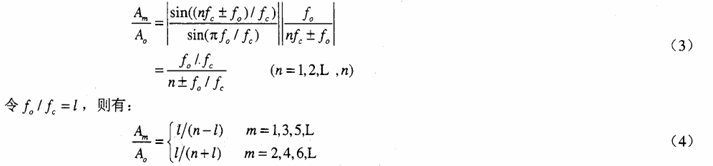

由式(2)可见,理想DDS的输出信号谱线仅存在于 n叱±%(n=o,1,2,L,n)。而且所有的谱线都在 sinc((六十矾)/‘7c)包络内,其频谱图如图1所示。 显然其频谱是一系列离散谱,而且在整数倍时钟频率 .f处没有谱线。镜像频谱分别位于够±.f(,z=1,2,L,,z) 处,第一镜像谱为.f一.£,镜像谱信号幅度与信号区主谱 线信号幅度关系有:

由式(3)和式(4)分析可得:

①!取值不能大于 1/2,即输出频率不能超过Nyquist 频率,最好也不要靠近 Nyquist 频率,否则难以与第一镜像频率分开:

②l的值越大,镜像频率与主频率幅度的比值越大,说明镜像频率所占的能量越大:相反,则主频谱集中的能量就多;

③ 当l=0时,广=0,此时可以认为输出能量全部集中在零频,而镜像频谱(整数倍f)的能量为零。

3跳频源方案设计

3.1原理分析

要实现快速捷变、低相位噪声、低杂散的高频段跳频信号源,需要综合考虑所选器件的性能指标、设计目标可实现性、原理可行性等因素。目前一般选用DDS和PLL作合成元器件,技术较为成熟,本设计就是基于 此方案设计的。

本设计目标是L波段跳频信号源,采用AD9858可以输出较宽带宽信号源,但不能直接使用,需要采用上 变频或倍频技术。将AD9858产生的较低频率信号提高到L波段,可以采用混频法,将频率提升;也可以使用 倍频技术,经过Ⅳ次倍频后,频率和带宽都变为原来的Ⅳ倍,从频率范围上看,能够满足设计要求,但考虑到 锁定时间较长,性能指标与单个器件相比,也有很大程度的恶化,因此本设计采用混频上变频方式。

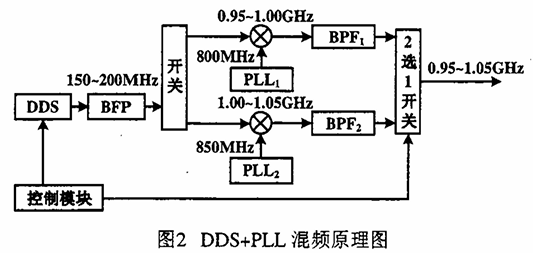

本设计要求跳频频率的绝对带宽为100 MHz,要让DDS输出入此宽的信号,产生的杂散丰富、谐波电平较 高。为了避免DDS因相位截断、幅度量化以及DAC非线性误差带来的影响,其带宽不可能选择太宽;而且根 据经验,一般最好避免跨越分数倍时钟及其附近的频点。为达到设计要求,我们设计了分段组合方式,即将需 要的频段分成两个较窄的带宽,这两个较窄带宽的频带宽度相同。该带宽是AD9858适合于本方案的最佳带宽, 在此带宽内各种性能指标相对较优。然后再与不同的本振源混频,最后把它们拼筹组合起来,即可得到需要带 宽频率。原理框图如图2所示。

其工作原理为:控制模块单元依据跳频图案找到相应的跳频频率,根据频率值的大小,决定选通PLL的那 一路信号和决定DDS输出频率的控制字,这些控制命令 与跳频图案有一一对应的关系。DDS经带通滤波器后由开 关控制分成两路信号,分别对应不同的频带,如图2所示。 当频率由某一值跳到另外一值时,如果超出该段带宽控制 的范围,则通过选择开关选择另外一路;如果没有超过该 路信号的频段,则继续使用该路信号。通过两路信号的组 合,从带宽上看即可满足我们的设计要求,产生L波段跳 ‘ 频信号源。

3.2 主要元罍件分析

本设计的核心器件是 AD公司的 AD9858 和 T公司的锁相环芯片 tf3761。AD9858是 2003年推出的一款高处理时钟、高性能的 DDS芯片,其主要特点是时钟频率高达1GSPS,输出信号频率最高可到450 MHz,是-款能够产生较高频段的信号源,在高时钟频率下可以通过改变频率控制字而较容易地改变输出频率,考虑性能指标等因素,可在 100 MHz内频率快速捷变。此外,该芯片还有4个频率控制单元,选择不同的频率控制单元可以输出不同频率的信号源,使得 AD9858 特别适用于跳频信号源的合成。其控制总线采用8位并行和串行输入两种输入方式,采用并行控制方式特别适合于需要高速控制的场合。

而 trf3761 则是 TI公司 2005年10月最新推出的一款适用于 GSM、CDMA、WCDMA 通信系统的高性能PLL。它集成锁相环(PLL)和压控振荡器(VCO)于一体,可控性好、性能指标优,最高输出频率可达1900 MHz,输出频率有分频比可选,基底相位噪声可达-160dBc/Hz@10MHz,最大鉴相频率可达30 MHz。本设计两个 PLL需要的频率分别为800MHz和850MHz,输出采用2分频方式(可以提高相位噪声指标),可以到达-126dBc/Hz@100 kHz的相噪指标。因此从元器件选择上看,完全可行。

3.3性能指标可行性分析

从快速频率捷变时间上看,如果前后两跳信号在同一通路的带宽内跳变,频率捷变时间由DDS的换频时间 决定;如果超出了该路带宽,将由DDs换频时间和开关切换时间共同决定。一般射频段的开关切换时间较快, 如AD公司的AD918,切换时间小于10 元间切换的时间最小可达3.5 ns;而DDs的频率捷变时间也在纳秒级,AD9858在4个频率控制单 ns,因此从频率捷变时间上看完全满足设计要求。

从杂散和相位噪声上分析,DDs芯片的相位噪声较优,输出103 杂散抑制优于.60 MHz时,相位噪声优于一140 dBc/Hz@1 kHz、 dBc。PLL如果作点频源时,不用考虑频率锁定时间,可以通过优化鉴相频率(PD)和环路带 宽(LP)来提高性能指标,该款PLL芯片(trf3761),相位噪声能够做到优于.90 dBc/Hz@1 kHz。因此DDs与 PLL经过混频后,性能指标有所恶化,但不会太大,最后再经过带通滤波器,滤出混频时产生的多次谐波与杂 散,最后指标能够做到:相位噪声优于.85

3.4控制软件设计 dBc/Hz@1 kHz、杂散抑制优于一50dBc,满足设计要求。

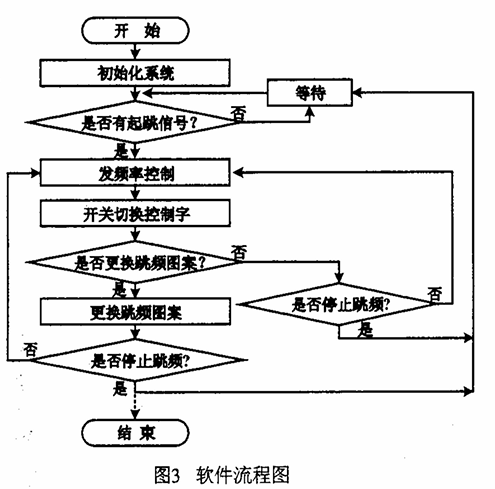

本设计的频率捷变时间短,要求控制在5“s以内,这就给控制电路提出了严格的要求。跳频频率表的查询、 DDS频率控制字的生成以及相应的开关切换命令都需要在较短的时间内完成,为此采用高速大规模逻辑芯片 FPGA予以实现。系统开机上电以后,首先初始化系统硬件——_DDs芯片初始化控制寄存器单元、PLL设定鉴 相频率和分频比,使PLL锁定各自的频率;然后依据跳频频率表,送DDS频率控制字和开关控制命令;检测 是否有中断命令,改变跳频频率表:检测数据是否发完,是否要停止跳频;最后结束跳频通信过程。其软件流 程图如图3所示。

4结束语

通过方案设计论证,我们给出了L波段快速跳频源设计方案,该方案跳频速率块、性能指标优,适用于军 事领域中抗干扰、抗截获、保密性好的通信场合。频率捷变速率快是本方案的难点和重点,可以对抗跳频图案 破解式跟踪干扰;载波在宽频带范围内伪随机跳变,频率可选性好,可以采用宽间隔跳频,避免阻塞式频段干 扰。经过硬件平台的调试,各项指标优良,均超过设计指标要求,说明方案可行。本设计是十五重大科研项目 的优化改进方案,通过优化,提高了各项性能指标,对整体跳频通信收发机的性能有很大提升。

参考文献

1 张广栋.C波段频率合成器的研制【D】.成都:电子科技大学硕士学位论文,2004.

2张伟.采用DDs+PLL技术实现的L波段频率合成器【J].微计算机信息,2005,(4).

3韩军功,王家礼.DDS频谱分析及一种新型的改善方法【J】.现代电子技术,2001,7:45—49.

4袁 伟,葛临东.DDS+PLL短波频率合成器设计【J].微计算机信息,2005,(9).

5郑长风,路青起,周 芸,等.基于直接数字频率合成的快速跳频通信信号源的设计阴.探测与控制学报,2005,(3)

售前咨询专员

售前咨询专员