技术分享

了解最新公司动态及行业资讯

存储系统中L波段射频直采技术设计与实现

0 引言

按标准的雷达频率命名法[1],L 波段是指1000~ 2 000 MHz 的无线电电波波段。 按传统实现方式[2],先采 用射频模拟下变频模块在模拟端将1000~2000MHz 变 频到100~1 100 MHz,然后采用低采样率的 ADC 进行信 号的采集。 此方法由于采用了大量的包括低噪放、滤波 器、衰减器和本振电路等模拟器件[3],考虑到模拟器件本 身易受干扰和有源器件容易引入噪声等因素,会大大降 低系统的无杂散动态范围(Spurious-Free Dynamic Range, SFDR)值,一般只能做到 50~55 dBFS。 本文提出了全新 的一种真正实现L波段全频段射频直采的设计方案,采 用超高采样率(采样率达到6GS/s)的 ADC 芯片实现射 频直采,不但简化了前端的采样电路,而且使SFDR 提 高到了65~70 dBFS。

1 存储系统中的射频采集存储方案

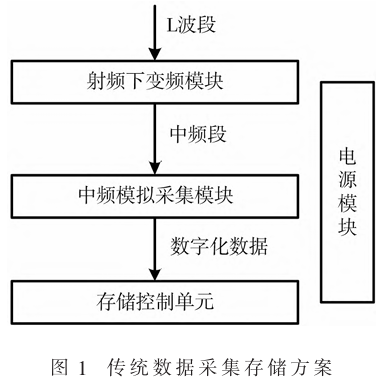

存储系统中传统的射频采集存储方案如图1所示。 从图1中可以看出,方案中主要板卡包括射频下变频模块[4]、中频模拟采集模块、存储控制单元和电源模 块等。 此方案不但使得存储系统变得复杂,板卡数量较 多,同时性能上受到了比较大的影响。

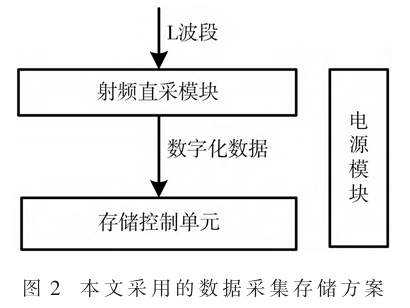

本 项目采用如图2所示方案,与图1对比可知,本方 案中少了射频下变频模块和中频模拟采集模块,取而代 之为射频直采模块,大大降低了前端电路设计的复杂度。 另外,射频直采模块主要由单片ADC+FPGA 架构组成, 硬件成本在5万元左右。 两个方案的成本相差大概在7.5 万元。

根据Nyquist 采样定理,fs ≥2fh [5],为了实现 L 波段的 全频段射频直采,采样率需要满足fs ≥4000MHz,为了 得到更好SFDR 性能,本文将采用 fs =6000 Mz 来实现 L 波段的全频段射频直采。 本文采用ADC芯片为ADI公 司的 AD9213BBPZ-10G。 该芯片支持最大的采样率为 10.25 GS/s,量化位数为 12 bit,最大接收带宽为 6.5 GHz (-3 dB),SFDR 值为 70 dBFS,接收带宽满足 L 波段的设 计需求。 下面描述具体设计实现方案。

2 射频直采方案硬件设计

2.1 时钟电路

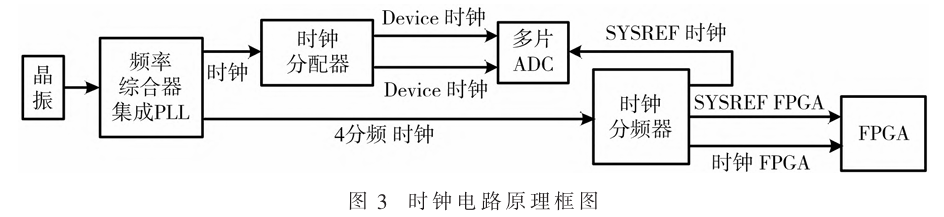

传统时钟电路采用超低抖动自带有支持JESD204B[6] 总线的专用时钟芯片实现,但是目前采样率已达6GS/s 以上,市面上单片的时钟芯片解决方案已无法满足需 求,需要采用多芯片级联构建的方式实现,具体实现框 图如图3所示。

多芯片级联构建电路有如下特点:

(1)支持 JESD204B 总线。

(2)输出的频率范围灵活可调,输出范围更宽。 既能 兼容单芯片的方案,也能满足采样率不断提高的使用 要求。

(3)具备高可塑性,通过简单的模块更换,可以实现更 高频率的输出,满足不同项目的不同采样率的使用需求。 频率综合器采用ADI 公司的ADF4372,单芯片集成 锁相环(Phase-Locked Loop,PLL),超低抖动值(38 fs)[7],输出通道有3路,其中一路最高输出频率为16000MHz, 剩余两路最高输出频率为8000MHz,内部集成固定分 频比电路,分别是1/2/4/8/16/32/64。 本设计中,采样率 设计为 6GS/s,ADF4372 输出 1 路 Device Clock 给时钟 分配器,由分配器分成多路Device Clock 送给多片 ADC 作为 ADC 的采样时钟。 时钟分配器采用 ADC 公司的 HMC987,支持最高工作频率为 8 000 MHz,可以将 1 路 时钟通过内部分配输出9路时钟。

时钟分频器采用TI公司的LMK04828,LMK04828 时钟 芯片是一款专用的JESD204B 超低抖动时钟芯片,Device Clock 和 SYSREF Clock 是成对输出的。 由于其最高输出 频率只能达到3080MHz,无法满足本项目的需求,但是 可以运用其内部的分频电路和SDCLK 和 DCLK 是成对 输出的特性,作为Clock FPGA 和 SYSREF FPGA 的输出 接口。

前端采用高频率稳定度的晶振,晶振频率为100MHz, 频率稳定度达0.5ppm。

整个电路工作原理如下:晶振产生的时钟输入给频 率综合器,频率综合器产生两路时钟,分别为6000MHz 和 1500 MHz,6 000 MHz 送给时钟分配器, 分配给多个 ADC 使用,1 500 MHz 送给时钟分频器,输出 SYSREF Clock、SYSREF FPGA、Clock FPGA 分别给 ADC 和 FPGA 使用。 此电路设计既保证了各时钟的同源性,又满足 了 ADC 采样时钟和 JESD204B 总线对不同频率时钟的 需求。

2.2 射频采集电路

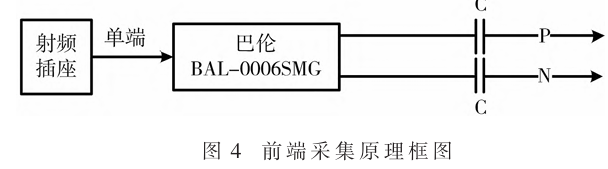

本文采用ADI 公司生产的最新ADC 器件AD9213 BBPZ-10G,为了减少前端模拟电路对采样性能的影响, 整个前端电路采用以巴伦为主要器件的无源器件搭建 而成,如图4所示,巴伦为一种三端口器件,实现将匹配 输入转换为差分输出而实现平衡传输线电路与不平衡 传输线电路之间的连接的宽带射频传输线变压器[8]。

输入的射频信号通过巴伦转换为差分信号后,再通

过交流耦合电容送给ADC 器件,耦合电容的值需要依

据实际工作频率值进行选取。 公式如下:

其中 f 为最小工作频率;Zc 为电容中的等效串联电阻 (ESR),一般小于 1 Ω。L 波段电路中优选 COG(NPO)材质 的大封装电容,大封装尺寸的比小封装尺寸的电容频率 特性要好。

2.3 FPGA 处理电路

ADC 器件的后端接入现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA),FPGA 选用 Xilinx 公司的 VIRTEX 7 系列 690T 芯片。 为了保证在全带宽模式下正 常工作,将 ADC 的 16Lane 接入 FPGA 的 GTH 总线上。 VIRTEX 7 系列 690T 芯片最多含有 80 GTH 收发器,最 高速率支持13.1 Gb/s, 满足 JESD204B 总线7.5 Gb/s 的 总线速率要求。

3 射频直采方案软件设计

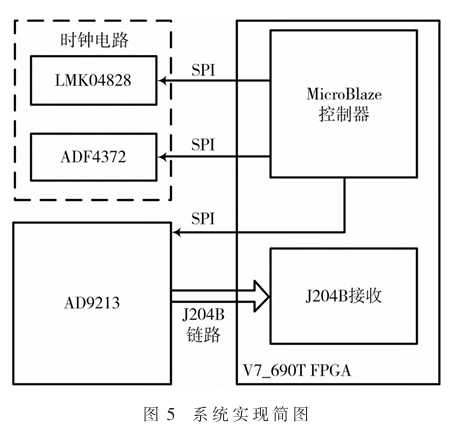

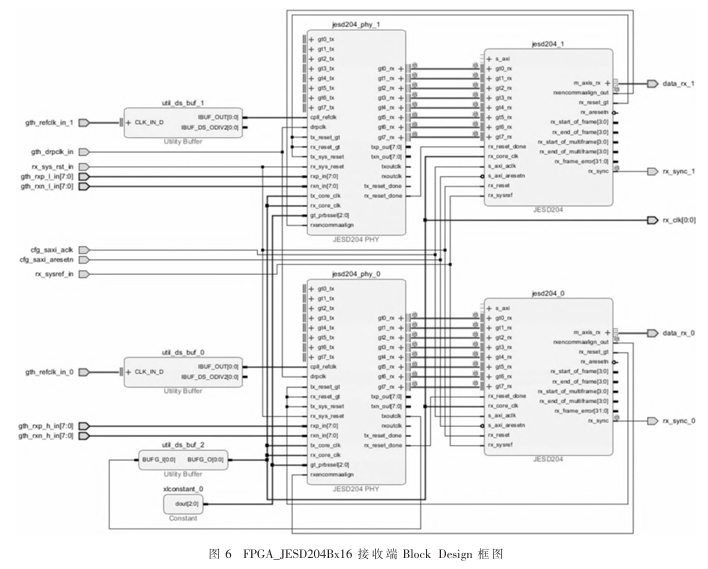

如图5 所示,本系统通过在V7_690T FPGA 内嵌入 MicroBlaze 处理器软核并运行配置控制程序实现对时钟 芯片ADF4372、LMK04828 和 ADC 芯片 AD9213 进行配置 控制。 利用 Xilinx JESD204 IP 核搭建如图 6 所示的 Block Design 框 图[9],实 现与 AD9213 JESD204Bx16 接口 对接,接口协议采用JESD204B Subclass1。

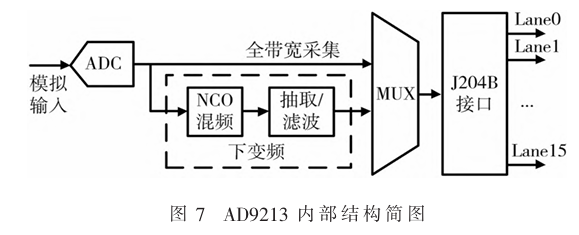

AD9213 内部结构简图如图 7 所示,其内部自带数字下变频(Digital Down Converter,DDC)功能模块,使用时可 以根据需求配置相关寄存器选择JESD204B 输出数据 源。 AD9123 可以预设 16 种固定中心频率,通过 GPIO 或 者SPI 寄存器进行切换,此种切换不需要对JESD204B 链 路重新进行同步,若需要设置其他非预设的中心频率,则 需要对JESD204B 链路进行重新同步操作,整体响应时间 较慢。 本设计为了灵活配置中心频率且加快响应速度, 使 AD9213 工作在全带宽采集模式下,在后端的 FPGA中实现DDC 功能。

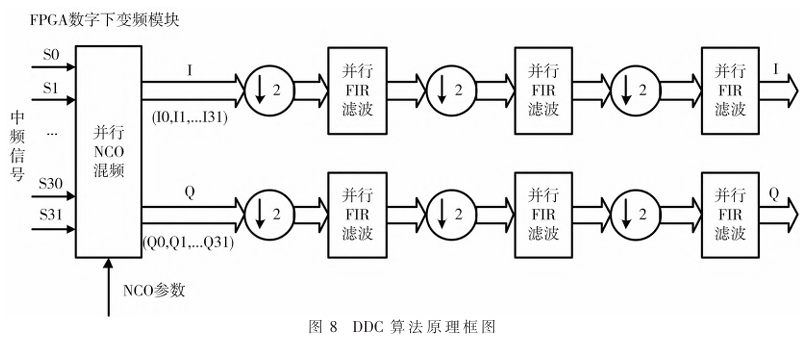

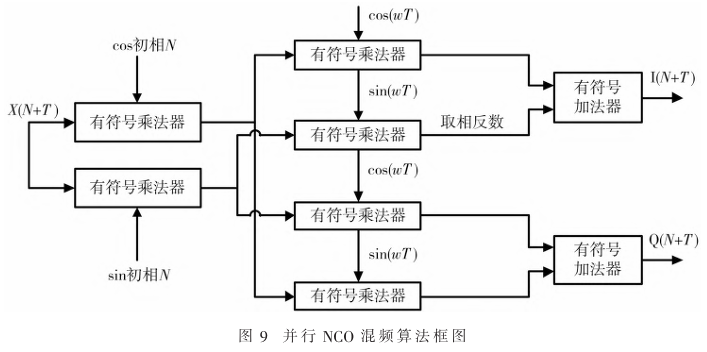

对JESD204B 接收的数据按照 JESD204B 协议标准帧 组成格式进行解析即可得到原始采集的中频信号。 FPGA 端实现 DDC 功能框图如图 8 所示,由于 AD9213 的采集带宽较大,若按照典型的单路数据进行混频运算 势必需要非常高的时钟频率,故需要采用并行NCO 混 频设计,然后对混频后的I、Q 数据结果进行并行滤波、 抽取。 根据使用效果将不同的NCO混频参数传递至并 行混频模块即可实现动态切换中心频率的效果。

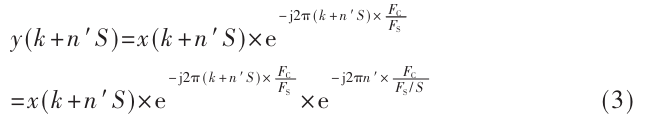

并行NCO 混频算法实现的原理推导过程如下[10-11]:

典型的混频运算数学公式如下:

其中FC 表示中心频率,FS表示采样频率。

当采样数据按照并行输入时,令n=k+n′S(k 为某时

刻的并行点序号,k=1,2,3,…,S;S 为并行采样点个数),则可到如下公式:

对上式进行三角函数展开即可得到如图9所示的 算法框图的计算过程。

4 系统性能分析和实测

在存储系统中,将前端射频直采的数据送至存储控 制单元进行存储,并通过存储控制单元的网络接口,可 以将已存储的数据进行快速地卸载到分析设备中,以 便于后续的数据分析和处理。当对1路射频模拟信号进 行直采时,采样率fs采用 6000MS/s,在 1 000 MHz 进行 全带宽采集时, 记录的存储带宽计算可得:6000MS/s× (12 bit/8)=9 000 MB/s,单路的存储带宽为9 000 MB/s;单 路按 1000 MHz 带宽进行数字下变频后所得 I/Q 数据 ( 抽取倍数 4 倍,采样率下降到 1500MS/s)可得采集存 储带宽为9000/4×2=4 500 MB/s。

整个系统选用Intel i7 CPU 控制器+FPGA 可编程逻 辑器件作为主控元件。 采用基于FPGA的高速串行总线 和 PCIE 互连技术的高性能存储系统构架实现数据的快 速传输。 详细实现框图如图10所示。

FPGA 自带的 GTH 高速串行总线接口按8.0 Gb/s 速率进行传输,每组 GTH X4 接口传输带宽理论可达4 GB/s,按 RapidIO 协议工作时的损耗,1 组 X4 接口实际 传输带宽具备3.2GB/s 传输能力,射频直采模块用 2 组 X4 RapidIO 接口的存储带宽可达 6 400 MB/s,满足前端 4 500 MB/s 的采集存储带宽。

射频直采模块将数据送往存储控制单元,存储控制 单元主要由Intel i7 CPU 控制器和 m.2 电子盘组成,m.2 电子盘采用 PCIE3.0 X4 接口完成高速的数据存储。 PCIE3.0 按 8 Gb/s 速率进行传输, 一组 PCIE3.0 X4 接口 传输带宽理论可达4000MB/s, 按 64%效率进行计算, 其实际可用带宽为2560MB/s,因此采用 2 组 m.2 电子 盘的存储带宽可达5120MB/s,满足前端 4500 MB/s 的 存储带宽。 因此整个系统的采集处理和存储同步进行 时,实时效率可达100%,能将采集的数据实时完全地存 储下来。

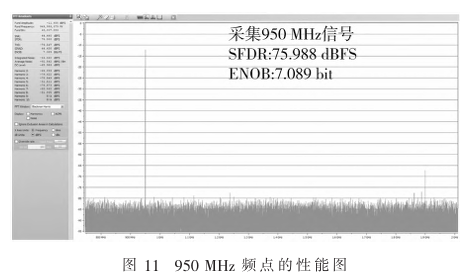

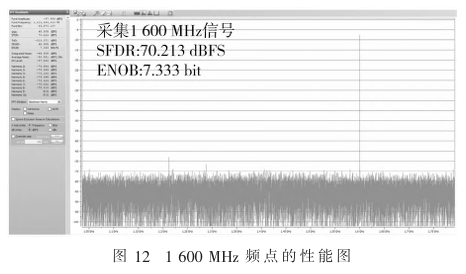

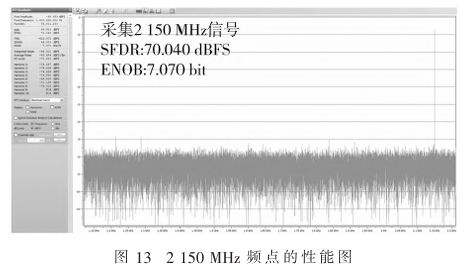

系统实际测试的数据如图11~图13所示,图中为 L 波段不同频点的射频直采频谱图,从图中可以看出,采用 本文的射频直采方案,可以将SFDR 值提高到67dBFS~ 75 dBFS,ENBO 可达 7.0 bit~7.3 bit。

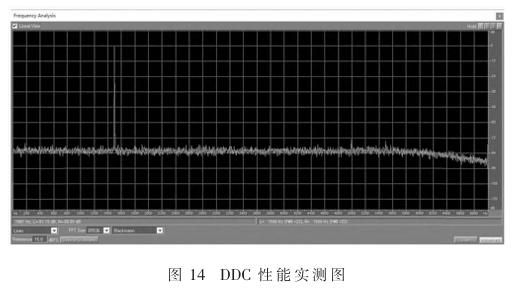

另外通过DDC 算法后的数据的性能如图14所示, SFDR 性能可达 70dB 以上, ENBO 可达 7.3bit。

经过对系统性能的测试,可以看出本文设计的6S/s 波段射频直采的存储系统在全频段上的SFDR 值依然 能保持在67dBFS 以上,可见系统具有良好的采样存储 性能。 本文采用了高性能的ADC、简单的前端电路设计 及低抖动的时钟电路等设计方案,最终实现高性能的L 波段射频直采的存储系统。

5 结论

本文介绍一种运用在存储系统中的L波段射频直 采设计和实现方案,对整体的硬件方案、软件方案分别 进行阐述,最后对系统的性能指标进行实际测试,测试 结果表明了系统的良好性能。 另外,整个方案在减少系 统复杂度、降低硬件成本的同时,提高系统的SFDR值, 为存储系统提供更加纯净的信号数据,同时也更有利于 后续的数据分析处理。

林文成,董郑宇,李 琼 ( 中国电子科技集团公司第五十二研究所,浙江 杭州310012)

参考文献

[1] SKOLNIK M I.雷达手册[M].王军,林强,米慈中,等译. 北京:电子工业出版社,2003.

[2] 周苏萍.基于 P 和 L 频段射频前端关键电路研究[D].杭 州:杭州电子科技大学,2011:4-32.

[3] 施福刚.L 波段收发组件的设计与实现[D].成都:电子科 技大学,2011:37-39.

[4] 安照辉.L 波段大动态范围的雷达接收机设计[D].成都: 电子科技大学,2017:7-17.

[5] ALAN V,OPPENHEIM A S,WILLSKY S,et al.信号与系

下一篇:试论软件无线电技术及其应用

售前咨询专员

售前咨询专员