技术分享

了解最新公司动态及行业资讯

应用于雷达干扰机的单比特测频算法研究和优化

摘 要:新体制雷达对抗技术的发展,对高宽带雷达信号的高速度、高灵敏度测频提出了日益 迫切的需求。接收机是一种常用的雷达干扰机,其测频模块作为雷达对抗技术的一大核心模 块,直接决定信号监测的覆盖带宽、信号处理的实时性以及灵敏度等方面。考虑到FPGA资源 的稀缺性,设计旋转因子,得到改进的单比特测频算法,避免传统的离散傅里叶变换过于依 赖大量乘法运算的不足。对0.2~2.2 GHz的随机频率正弦信号进行测试,未过度引入误差,且 大幅优化了时间和空间复杂度。在新型RFSoC平台下编写Verilog代码进行实际测试和仿真优 化,对比了基16到256的单比特测频性能。实验结果显示:权衡响应速度及灵敏度,基64的单 比特测频最适合2 GHz带宽的雷达干扰技术需求,可以做到-50 dBm的灵敏度、18.75 MHz的 最大频率精度误差;在低于100 ns的测频时间内,实现了对2.4 GHz的宽带信号的快速测频。

关键词:雷达对抗技术;干扰机;RFSoC平台;单比特测频算法;基64

0 引言

目前,新体制雷达对抗技术迅速兴起和发 展,对雷达干扰机的功能、性能等提出了更严格 的要求,不仅要做到小型化、低成本、低功耗, 而且要易于实现多机并行和规模化部署,还需要 具有更广的带宽覆盖面、更高的截获灵敏度和更 快的信号处理速度,以持续提升电子对抗水平。

现有的一种有效的雷达对抗策略是令多台干

扰机同时工作,在空间上形成一个三维的结构,

对敌方雷达进行立体式全覆盖的干扰。这是一种

灵活的部署方略,其首要前提是设备体积重量的

减轻、功耗成本的降低和计算速度的提升。接收

机是一种常见的干扰机,测频是其关键环节。多

通道并行拼接而成的接收机虽然能够提供高精度

的模拟数字转换器(ADC)、数字模拟转换器

(DAC)和高保真的数字通道以保证测频的精度

和速度,但无法满足上述前提,故难以在目前的

雷达对抗体系中推广普及。因此,亟需找到一种

新型的硬件架构以及开发配套的有效算法,以更

好满足当前的雷达对抗需求。

单比特测频算法是一种有效的信号侦察检测 算法,文献[1]首次提出了该概念。2002年左右, 有学者采用专用集成电路(ASIC)开发出一个小 型化的单比特接收机,实现了频域处理,测频精 度为5 MHz,瞬时带宽为1 GHz。2013年,段国 文[2]在FPGA芯片SC5VSX95T上实现了10 Gs/s的 采样率、256点的单比特测频,但其缺点是占用硬 件资源较多,且延时较长(约为500 ns)。2021 年,文富忠等[3]在10 Gs/s的采样率下研制了一个 具有16 GHz瞬时带宽的单比特接收机,延时优化 到小于270 ns。2020年,杨一鸣等[4]对一款采样率 为20 Gs/s的单比特接收机进行了仿真验证,验证 了其在电子对抗中的应用价值。2021年,季鹏飞 等[5]使用一片FPGA芯片XC7K410TFFG676、一 片采集芯片AAD01S404G及其外围电源模块,研 制了超宽带、小型化的单比特接收机,缺点在于 牺牲了信号的检测灵敏度,仅为-4~14 dBm。

单比特测频算法的最大优势在于测频速度 快、对信号的灵敏度高、测频精度高。相较于传 统的接收机,使用单比特测频算法的接收机可以 对宽带、小体积信号实现高性能的接收和处理,可以独立、快速地实现雷达信号瞬时频率、脉冲 宽度、脉冲到达时间等脉冲特征参数的提取。但 是,该算法的量化位数为1,具有非线性的特性, 交互调制和谐波问题较多,动态范围也较小,对 于两个同时到达的信号,只能检测出其中的最大 信 号[6]。为更好满足雷达对抗技术的持续发展对 雷达侦察快速处理及准确性提升提出的更高要 求,尽可能节约硬件资源和提高接收机判断能 力,本文依托于一种FPGA平台——新型RFSoC 平台,对单比特测频算法进行研究和优化。首 先,介绍单比特测频算法基本理论与技术特点; 然后,通过Matlab对单比特测频算法与传统的离 散傅里叶变换在噪声特性上的差异进行仿真和研 制;最后,在新型RFSoC平台上实现单比特测频 算法,对不同阶数的单比特测频资源和时间占用 进行考察,优选出最适合于干扰机的阶数。

1 单比特测频算法基本理论与技术特点

单比特测频算法的核心是采用近似的离散傅 里叶变换进行快速的信号测频,这正是单比特测 频算法赖以发挥快速、高灵敏度、低虚警率等优 势的根源所在[7-9]。

干扰机需要在处理时间和硬件资源两个方面 之间进行权衡[10-13]。由于雷达信号一般属于宽带 信号,且在FPGA中DSP资源一直十分紧张,因此 有必要对其基本理论进行深入剖析。

传统的离散傅里叶变换公式为

其中,信号 与旋转因子

与旋转因子 的乘法会造成大量的运算。旋转因子

的乘法会造成大量的运算。旋转因子 的表达式为

的表达式为

由此可见,旋转因子  是复数浮点值,

会涉及多种不同的复数值,进而会使得复数乘法

运算量非常浩大,对于运算时间和FPGA资源的消

耗都很大。

是复数浮点值,

会涉及多种不同的复数值,进而会使得复数乘法

运算量非常浩大,对于运算时间和FPGA资源的消

耗都很大。

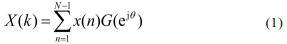

单比特测频算法的旋转因子简化示意图如图1 所示。传统的离散傅里叶变换的旋转因子是以极 坐标的零点为圆心的圆上的点,但若只考虑坐标 轴上的4个点,旋转因子就只有+1、-1、+j、-j, 将一定范围的旋转角度全部量化成一个比特就能表示的数,即

由此,算法本质上从复数乘法运算变为门限判决,这样就可以避免耗时的乘法运算并避免在 FPGA中占用过多DSP资源。

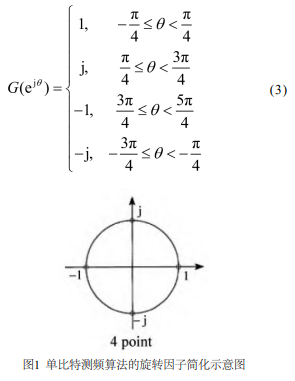

对算法性能进行简要分析。按照接收机灵敏度 计算公式

计算公式

其中:B 为接收机接收到的信号带宽,单位是 MHz;NF为接收机的噪声系数;M是能够保证接 收机正常工作的最小信噪比,又称检测系数。一 般来说,干扰机的检测系数一般为14 dBm,噪声 系数在这里取6 dBm。

数据经过单比特运算过程会有1 dBm的功率损 耗,所以检测信号的灵敏度可以达到约-60 dBm, 能够接收2.4 GHz的带宽信号。若采用基64的单比特 测频算法,则每一个频率单元的带宽是37.5 MHz。 在每一个信道内进行时域信号检测,则每个信号 的检测带宽应是37.5 MHz,最大误差不会超过 18.75 MHz。

2 单比特测频噪声特性仿真验证

由 第1章可知,单比特测频算法属于简化计 算,相较于传统的离散傅里叶变换,势必会多引入一些误差,那么它抵御现场模拟噪声的能力如 何,与传统的离散傅里叶变换相比抗噪特性如 何,也有待进一步论证。

利用Matlab生成带宽处于0.2~2.2 GHz的随机 频率正弦信号,并引入噪声分量。一般来说,在 常见的RFSoC中,由ADC引入的噪声变量是由采 样时钟和输入信号的二次谐波造成的。当输入频 率为0.2~1.2 GHz时,带内噪声主要是输入信号的 二次谐波;当输入频率为1.2~2.2 GHz时,带内噪 声主要是4.8 GHz的采样时钟减去输入信号的二次 谐波。所以,在仿真中加入的噪声变量,相较于 主频有6 dB的衰减。

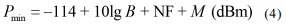

由单比特测频算法和传统的离散傅里叶变换 计算出来的频谱如图2所示。显而易见,利用基64 的单比特测频算法和传统的离散傅里叶变换测量 同一个信号,结果的耦合度很高,二者的误差分 布并不严重。

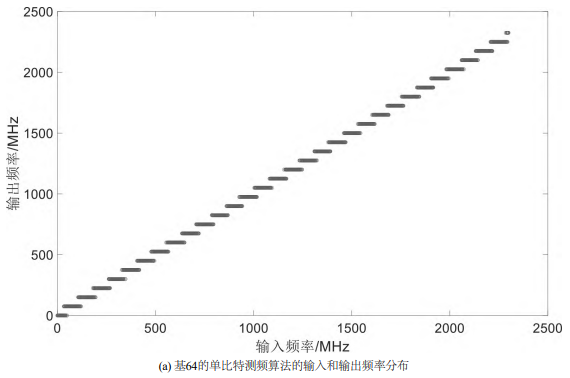

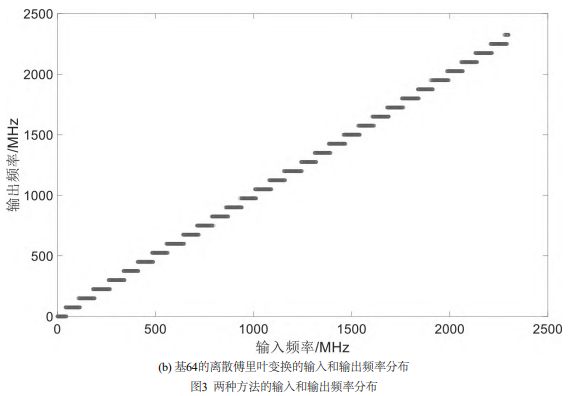

再利用Matlab随机生成10 000个随机频率的信 号。利用两种方法检测得到的输出和输入分布分别 如图3a和图3b所示。显而易见,两种方法的误差分 布基本是一样的,最大误差为18.75 MHz。同时, 这两种方法所得误差基本上分布于每一个点的边 缘,误差并没有明显的扩大。由此可以认为,用 单比特测频算法替代传统的离散傅里叶变换,并 不会引入较大的误差。

综上,经论证,单比特测频算法能够在牺牲一定抗干扰能力的情况下,达到既优化运算时间 复杂度,又优化空间复杂度的目的。况且,在实 际的RFSoC中,ADC采样信号的杂散一般可以被 优化到50 dB以下,并不会出现这么大的杂散功 率,而且当环境中有多个雷达辐射源存在时,雷 达信号特征一般会有一定的频率差,保证不同的 辐射源之间不会相互干扰,所以以上误差也只是 一种极端情况。基本可以证明,使用单比特测频 算法代替传统的离散傅里叶变换作为雷达干扰机 的核心算法,是不存在问题的。

3 基于新型RFSoC平台的单比特快速 测频算法实现和优化

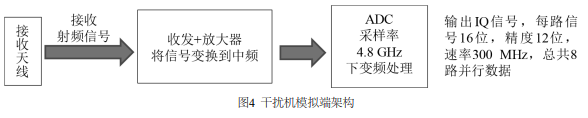

雷达信号的频谱范围极宽,小到0.1 GHz,大 到18 GHz。要处理这么广的带宽,需要先在模拟 域进行数字信道化,将雷达信号分为若干个中频 信号,再进行离散数字处理。雷达干扰机接收端 架构如图4所示。从接收天线传送出来的模拟信号 经过收发模块处理之后,变为中心频率1.2 GHz、 带宽2 GHz的中频信号;利用4.8 GHz采样率的芯 片内部集成的ADC模块的一区采样,可以保证信 号不失真,使得采样一区的杂散低于50 dB。

输入ADC中的射频信号变换为离散的数字采 样信号后,再将采样的数据传送到FPGA中,进行 雷达脉冲信号的截获、校验、计算、比对,最后输出测频结果。

本文干扰机的优势在于FPGA主芯片采用了 AMD公司UltraScale+系列的RFSoC,芯片中集成 的直接射频采样数据转换器消除了对外部数据转 换器的需求,将大部分射频信号处理过程转移到 数字域,是一种灵活的射频解决方案。与多组件 解决方案相比,功率和占地面积减少了50%。

相比于数字信号处理中常用的 AD9361 加 Virtex-7的数字板架构,新型RFSoC架构通过集成 ADC和DAC,减小了芯片面积,并降低了数字板 上电源树和时钟树的设计难度,从而减小了干扰机 的总体积。同时,在传统的AD9361加Virtex-7的数 字版架构中,由于PCB工艺等的限制,难免会使得 不同路数字信号之间产生大小不等的延时,每一块 数字板都需要进行人工校准,且即使如此,在极端 温度条件下依然还会难免产生延时。而RFSoC集成 了上述全部功能,可以避免上述问题,还可大大节 约后续的人工成本和测试成本。

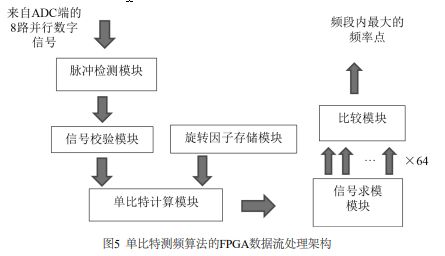

单比特测频算法在FPGA内实现的信号数据流 处理架构如图5所示。

经过高速ADC采样后的数据,是主时钟频率 为300 MHz的8路并行数字信号,具有12比特的数据精度。当ADC正常工作时,接收到的信号进入 脉冲检测模块,进行包络计算,只有超过检波值 的包络信号才会被视为有效的脉冲信号。判断为 有效的脉冲信号进入信号校验模块,排除因为抖 动造成的误判。

接着,通过读取储存于旋转因子存储模块中 的旋转因子,将每一位IQ信号分别变为原码、反 码和0。8路并行数据的IQ信号分别依次相加,得 到信号的累加值。将结果送入信号求模模块,求 虚部平方与实部平方的和。最后,总共64路的结 果通过比较模块进行大小比较,最大者即为频段 内最大的频率点。

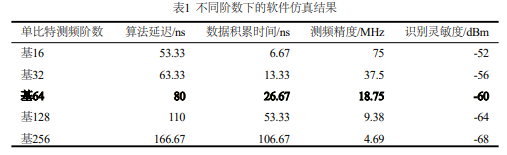

Verilog代码的核心思想就是将信号分别与64 个不同的旋转因子分别计算,经过累加后再进行 比较。根据以上思想编写代码,通过更改旋转因 子的配置参数和数据积累时间等,变更单比特测 频阶数,验证不同的阶数下的延时、测频精度、 识别灵敏度等,如表1所示。

如 表1所示,单比特测频阶数越高,测频精 度越高,但对应的时间复杂度(算法延迟)也就 越大。为了给后续的信号处理模块预留足够的时 间,一般来说,干扰机测频最大时间在100 ns之内较为合适。综合来看,基64的单比特测频既保 证了一定的测频精度,又不会过多地占用处理时 间,是最为合适的阶数。

相较于FPGA内的其他测频手段,例如AMD官 方提供的1 024个点的快速傅里叶变换,虽然也可 以实现很高的测频精度,但是会大大占用逻辑资 源,且算法延迟高达7 μs,这对于捷变频雷达信号 而言严重滞后,这就使得雷达脉冲到达保护目标并 产生回波的时间过长,此时再实施电子对抗技术已 经变得毫无意义。因此,本文研制的雷达干扰机单 比特快速测频算法是十分重要和必要的。

4 结束语

为了满足新体制雷达对抗的实时性要求和 节约硬件资源、占地面积的需求,本文通过 Matlab,利用单比特测频算法,对引入噪声分量 的信号进行了处理,评估了其成本效益;基于新 型RFSoC平台,使用Verilog代码,对单比特快速 测频算法进行了实现和优化,综合考虑硬件占用 情况和干扰机的性能要求,找到了最为合适的配 置参数。

本文结果表明,在新型RFSoC平台下使用基 6 4的单比特测频算法,满足最小误差要求、处 理速度要求、硬件资源占用要求、处理信号的带 宽要求等,可以较好适应目前雷达对抗技术的要 求。相比于传统的单比特接收机,本文在RFSoC 平台上实现的单比特测频算法无疑在性能、体积 和开发成本等方面具有相当的优势,在新体制雷 达对抗领域具有广泛的应用前景。

参考文献

[1] POK D, CHEN C. Chip design for monobit receiver[J]. IEEE Transactions on Microwave Theory & Techniques, 1997, 45(12): 2283-2295.

[2] 段国文. 采用MonoDFT测频的单比特接收机性能分析. 电 子技术应用, 2013, 39(11): 96-98.

[3] 文富忠, 胥全春, 韩学涛, 等. 一种超宽带电子战测频技术 的研究[J]. 遥测遥控, 2021, 42(1): 56-63.

[4] 杨一鸣, 向海生. 一种单比特测频接收机的设计与仿真[J]. 舰船电子对抗, 2020, 43(3): 119-122.

[5] 季鹏飞, 刘福元, 杨志远, 等. 一种超宽带小型化单比特测 频接收机的设计与测试[C]//2021年全国微波毫米波会议 论文集: 上册. 中国电子学会, 2021: 296-298.

[6] 王一舒, 沈凤臣. 补偿矩阵测频算法在单比特多波束测 向中的应用[J]. 中国电子科学研究院学报, 2017, 12(3): 285-288.

[7] 石荣, 阎剑, 张聪. 基于随机抖动的单比特量化理论分析与 仿真研究[J]. 现代电子技术, 2013, 36(3): 63-66.

[8] 焦瑞涛, 林晓烘, 叶灵军, 等. 基于单比特量化的低截获雷 达信号测向方法[J]. 舰船电子工程, 2019, 39(11): 79-83.

[9] 周涛. 量化精度对数字化接收机性能的影响[J]. 电子信息 对抗技术, 2006, 21(6): 20-23.

[10] 吕远, 唐斌, 祝俊. 一种基于高阶近似核DFT的快速实现算 法[J]. 电子信息对抗技术, 2009, 24(2): 19-22.

[11] 张硕, 梁士龙. 单比特测频接收机中DFT算法的优化[J]. 制导与引信, 2006, 27(2): 51-55.

[12] TSUI J. 宽带数字接收机[M]. 北 京: 电子工业出版社, 2002.

[13] 季鹏飞. 单比特测频接收机的研究与设计[D]. 长沙: 国防 科技大学, 2017.

张宇祥,黄明,杨杰,郭宇航,周元翰 (北方工业大学工学院,北京 100144)

张宇祥(1999—),男,研究生在读。研究方向:雷达信 号侦查和分选。 E-mail: 13552983080@163.com

黄明(1977—),通信作者,男,高级实验师。主要研究 方向:弱信号采集与数字信号处理。 E-mail: huangmingncut@126.com

杨杰(2001—),男,电子信息工程专业本科生在读。主 要研究方向:弱信号采集和数字信号处理。 E-mail: 1906920251@qq.com

郭宇航(2002—),男,电子信息工程专业本科生在读。 研究方向:弱信号采集和数字信号处理。 E-mail: 2976568613@qq.com

周元翰(2001—),男,电子信息工程专业本科生在读。 主要研究方向:数字信号处理 E-mail: 2860303832@qq.com

Research and Optimization of Monobit Frequency Measurement Algorithm Applicable for Radar Jammer

ZHANG Yuxiang, HUANG Ming, YANG Jie, GUO Yuhang, ZHOU Yuanhan (College of Engineering, North China University of Technology, Beijing 100144, China )

Abstract: With the development of new radar countermeasure technology, there is an increasingly urgent demand for high-speed and high-sensitivity frequency measurement of broad-bandwidth radar signals. Receiver is a commonly used radar jammer, and its frequency measurement module, as a core module of radar countermeasure technology, directly determines the coverage bandwidth of signal monitoring, the real-time performance and sensitivity of signal processing. Considering the scarcity of FPGA resources, a rotation factor was designed to obtain an improved monobit frequency measurement algorithm, which avoided the deficiency that the traditional discrete Fourier transform relied too much on a large amount of multiplication operations. The random frequency sine signal of 0.2~2.2 GHz was tested, showing that the error was not excessively introduced, and the time and space complexity were greatly optimized. The Verilog code was written on the new RFSoC platform for actual test and simulation optimization, and the monobit frequency measurement performances of Base 16 to 256 were compared. The experimental results show: considering the response speed and sensitivity, the monobit frequency measurement of Base 64 is most suitable for the technological requirement of radar jamming with 2 GHz bandwidth, and can achieve the sensitivity of -50 dBm and the maximum frequency accuracy error of 18.75 MHz; in the frequency measurement time less than 100 ns, the fast frequency measurement for the 2.4 GHz bandwidth signal is realized.

Keywords: Radar Countermeasure Technology; Jammer; RFSoC; Platform; Monobit Frequency Measurement Algorithm; Base 64

售前咨询专员

售前咨询专员