技术分享

了解最新公司动态及行业资讯

基于软件无线电的通用 SoC 平台设计

李 研 (西安导航技术研究所,西安 710068)

摘 要:针对专用集成电路(ASIC)扩展性差、不能灵活配置的问题,提出了一种基于软件 无线电(SDR)的通用 SoC 架构,该架构具有模块化程度高、扩展性强以及软件灵活可配的优点。 相比于 ASIC 架构,增加了处理器、存储器、多主机总线以及直接存储器存取(DMA)等模块, 完成了 SDR SoC 架构下的系统集成,仿真验证了采用该架构后芯片功能正常且性能不受影响, 同时不会增加过多的时钟延迟和资源消耗。

关键词:软件无线电;多主机总线;直接存储器存取;SoC

Design of General SoC Platform Based on Software Radio

Abstract: Aiming at the problem of poor expansibility and inflexible configuration of Application-Specific Integrated Circuit (ASIC), a general SoC architecture based on software radio is proposed, which has the advantages of high modularity, strong expansibility and flexible software. Compared with the ASIC architecture, the processor, memory, multi-master bus and Direct Memory Access (DMA) are added, and the system integration under the Software Define Radio (SDR) SoC architecture is completed. Simulation verifies that the chip functions normally and the performance is not affected after adopting the architecture, while not significantly increasing clock delay or resource consumption.

Key words: Software Define Radio; Multi-Master Bus; DMA; SoC

0 引言

随着信息技术和集成电路产业的飞速发展,专 用集成电路(Application-Specific Integrated Circuit, ASIC)芯片已经渗透到了军工、民用等多个领域, 成为推动科技创新和产业升级的重要力量[1]。然而, 定制化设计在带来体积小、功耗低等优势的同时, 也引发了新的挑战,如开发成本高、周期长、风险 大等缺点,尤其在通用化方面的问题日益凸显。 ASIC 芯片对算法依赖性高,在设计完成后其内部 逻辑和芯片功能就固定了,流片制造后无法进行更改,而一旦算法发生变化就需重新设计完整的电路 结构,耗费大量的人力和物力。为了克服上述问题, 各大芯片厂商开始探索新的通用芯片设计理念和 技术途径。

软件无线电(Software Defined Radio,SDR) 是由 Mitola 博士在 1991 年提出的一种可重新编程 的无线通信新概念[2-3],在微电子领域能显著提高 SoC 芯片的通用性和适应性,推动其向高集成度、 灵活性和可编程性方向发展。

目前国内外已有许多将 SDR 架构应用于芯片 设计的成功案列,美国 Qualcomm 公司发布的全球 首款 5G modem 芯片 Snapdragon X50 是一款集成 了 SDR 功能的芯片,支持 5G 和 4G LTE 等多种无 线通信标准[4]。美国 ADI 公司推出的 AD9361 和AD9364 都是用于无线通信的射频收发器芯片,支 持多频段和多种通信标准[5]。芯纪元科技设计的多 模导航 SoC 芯片,通过单个模拟接收通道处理多个 不同频率不同制式的导航信号,在不影响芯片性能 的同时极大降低了模拟电路的规模[6]。城芯科技的 CX9261 基于软件无线电理念设计,片内集成射频 ( Radio Frequency , RF )、模数转换器 (Analog-to-Digital Converter,ADC)/数模转换器 (Digital-to-Analog Converter,DAC)以及数字上 下变频等电路,极大减少了射频链路设计的复杂度, 系统集成度高,实现国产化功能替代 AD9361[7]。

本文针对 ASIC 芯片扩展性差的问题,研究基 于 SDR 的通用 SoC 芯片架构,聚焦于搭建可扩展 多主机总线结构,以直接存储器存取(Direct Memory Access,DMA)为主控制器,对总线上挂 载的快速傅里叶变换等信号处理加速 IP 进行调度 控制,完成基于 SDR 的通用 SoC 平台设计。

1 SDR SoC 架构

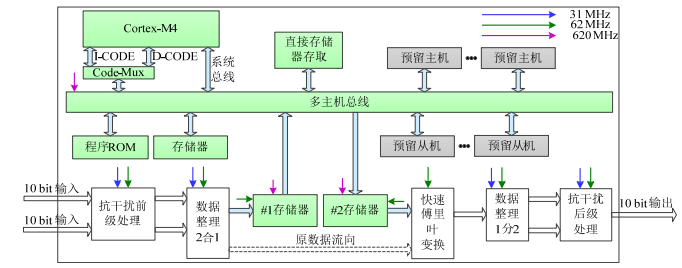

本文设计的 SDR SoC 架构如图 1 所示。

图 1 SDR SoC 架构

原有的专用化芯片包括抗干扰前级处理模块、 数据整理 2 合 1 模块、快速傅里叶变换模块、数据 整理 1 分 2 模块以及抗干扰后级处理模块,芯片输 入是射频信号经模拟下变频及模数转换后的两路 10 bit 中频信号,经过抗干扰处理后输出 10 bit 信号, 完成抗干扰处理。本文在原有架构基础上,采用模 块化设计思想,新增 Cortex-M4 处理器,DMA、多 主机总线以及存储器等模块,打断原数据流向,将 数据整理 2 合 1 模块和快速傅里叶变换模块通过存 储器挂在多主机总线上,使用 DMA 模块实现高速 数据的控制和搬移。相比于原 ASIC 架构,该 SDR SoC 架构具有更强的可扩展性和灵活性,模块化程 度更高,能适应不同的应用场景。

2 多主机总线矩阵设计

传统总线由于其固定的架构和有限的带宽,存 在着扩展性差、设计复杂的问题。随着总线上主从 设备数量快速增加,传统的总线结构将达到性能极 限,无法提供更高的带宽、更低的延迟以及更好的 系统设计灵活性[8]。为此本文通过脚本自动生成基 于高级高性能总线(Advanced High-performance Bus,AHB)接口的多主机总线矩阵。

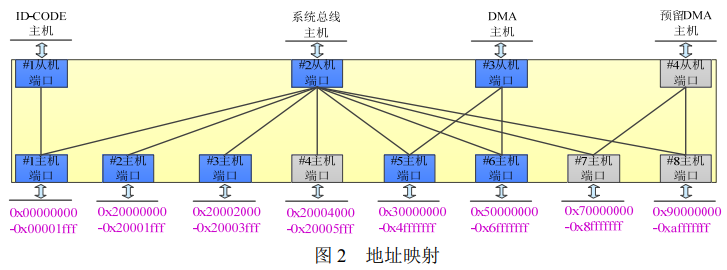

根据图 1 的 SDR SoC 架构,设计的多主机总线 矩阵地址映射关系如图 2 所示。

图 2 中有 4 个从机接口,其中 3 个分别连接 Cortex-M4 的 ID-Code 总线和系统总线,以及 DMA 主机,此外预留了 1 个从机接口,有 8 个主机接口, 其中 5 个分别连接程序只读存储器(Read-Only Memory,ROM)、存储器、DMA 从机、数据整理 2 合 1 模块以及快速傅里叶变换(Fast Fourier Transform,FFT)模块,剩余 3 个为备用接口。

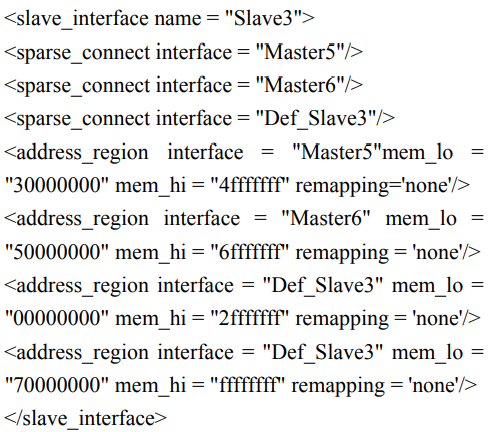

根据地址映射关系修改,采用固定的地址映射 关系进行设计,无重新映射,编写每个 slave 接口 的连接情况,得到 AhbMtx.xml 脚本,部分脚本实 现如下:

Slave3 分别与 Master5 、 Master6 以 及 Def_Slave3 连接,需先声明与其连接的每个接口, 再编写每个接口分配的地址空间。编写完脚本后, 在 Linux 系统下运行 perl bin/BuildBusMatrix.pl -xmldir xml-cfg AhbMtx.xml-over-verbose 命令,生 成数据位宽 32 bit,地址位宽 32 bit 的多主机总线矩 阵,如图 3 所示。

3 AHB DMA 设计

为有效解决 SDR SoC 架构下各模块之间频繁 且大量数据交互的需求,本文采用 DMA 技术[9-10], 以实现高效、高速的数据传输。该技术绕过中央处 理器(Central Processing Unit,CPU)直接在内存 和设备之间传输数据,提高 CPU 的利用率,同时 可以为片内模块间的协同工作提供强有力的支持。 DMA 的主要特征包括:

1)支持 AMBA2.0 AHB 总线协议;

2)包含 1 个数据传输通道。该通道拥有全 32 位的寻址能力;

3)数据尺寸大小支持字节、半字和字;

4)突发传输结构可编程。支持 1、4、8、16 拍传输结构;

5)具有中断产生功能。数据搬移完成后会产 生中断信号。

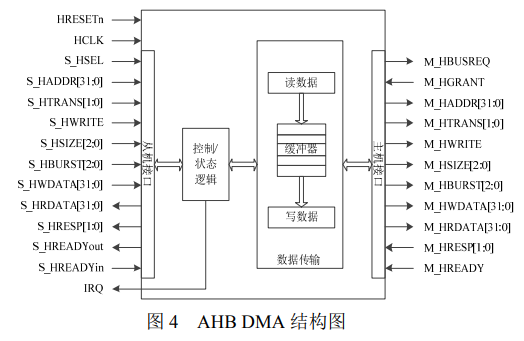

DMA 的具体结构如图 4 所示。

该模块主要包括 AHB 从机接口、AHB 主机接 口、控制/状态逻辑(Ctrl/Sta Logic)以及数据搬移 器(Data Mover)。通过从机接口 M4 处理器可以 对 DMA 内部控制和状态寄存器进行读写操作,通 过主机接口 DMA 模块可以控制管理挂载在总线下 的各模块间的数据传输。

AHB DMA 进行数据搬移主要包括通过数据搬 移器完成,每次数据传输都包括一次读数据搬移和 一次写数据搬移,在控制/状态逻辑的控制下,DMA 以内存映射的方式从源地址读取数据暂存在缓冲 器,再以内存映射的方式将数据写到目标地址空间, 在搬移完处理器指定的字节数后,DMA 会产生一 个中断请求信号(Interrupt Request,IRQ)。

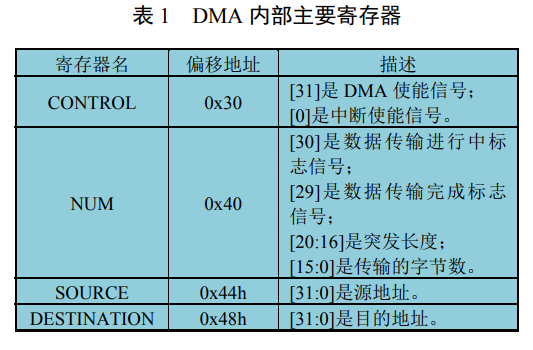

DMA 内部的几个主要寄存器定义如表 1 所示。

根据寄存器地址及功能进行软件设计,部分软 件代码如下:

while(1)

{

*((volatile uint32_t *)dma1_en)=0x80000001;

*((volatile uint32_t *)dma1_src)=0x30000000;

*((volatile uint32_t *)dma1_dst)=0x50000000;

*((volatile uint32_t *)dma1_num)=0x80012000; //2048*4 BYTE

}

4 仿真实验

本文所有功能模块均采用 Verilog 语言进行寄 存器传输级设计,在 Linux 环境下实现系统集成, 同时根据芯片功能,使用 VCS 2018 和 VERDI 2018 搭建仿真平台,编写测试激励进行仿真,最后对 SDR SoC 进行抗干扰性能、延时以及资源消耗分析。

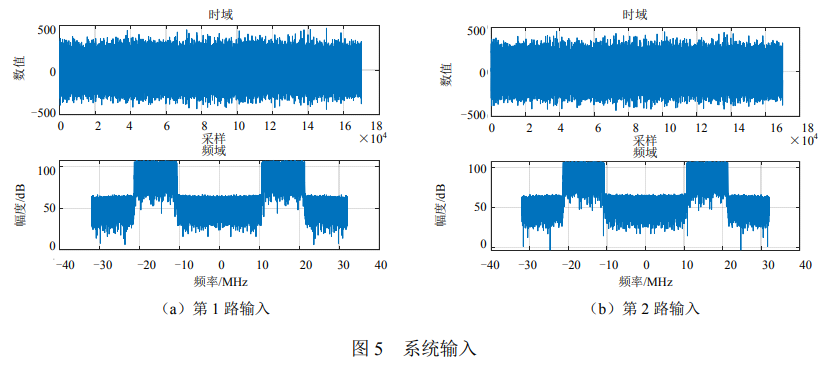

使用 Matlab 产生 2 路 10 bit 满量程干扰作为系 统输入,干扰带宽为 10 MHz,区别于系统滤波器 的 20 MHz 带宽,2 路输入如图 5 所示。

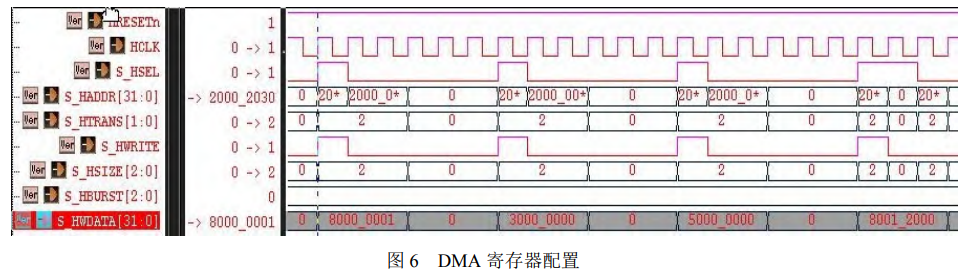

M4 处理器通过 DMA 从机接口对内部寄存器 进行配置的过程如图 6 所示。在 S_HSEL=1 和 HWRITE=1 时,依次向 DMA 基地址 0x20004000, 偏移地址为30、44、48、40的寄存器写入数据0x 80000001、 0x 30000000、0x 50000000、0x 80012000,表示开 启 DMA 使能,开启中断使能,源地址是 0x 30000000, 目标地址是0x 50000000,突发长度为1 拍,传输字节 个数为 8 192。

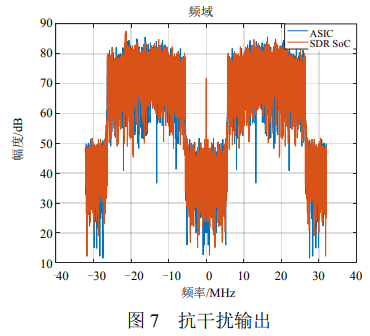

抗干扰输出如图 7 所示,频域波形具有 20 MHz 带宽的滤波器特性,10 MHz 带宽的干扰被抑制,抗干扰功能正常,且 SDR SoC 与原 ASIC 性能相当。

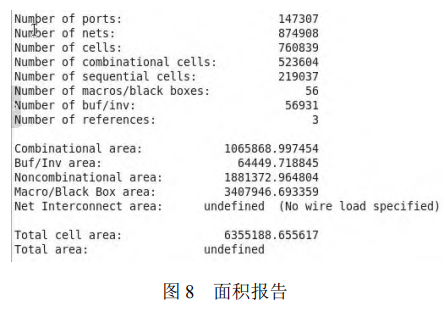

使用 Design Compiler 进行逻辑综合,目标库选 择中芯国际 55 nm 工艺库,得到面积报告如图 8 所 示,总面积是 6 355 188 2 μm 。相比于原 ASIC,SDR SoC仅增加了112 394 2 μm 的面积和13个时钟延时, 取得了资源和性能的平衡,符合预期效果。

5 结语

本文完成了基于 SDR 的通用 SoC 平台设计工作,仿真验证了 SDR SoC 功能正常且性能不受影响, 相比 ASIC 架构,SDR 架构支持高性能成熟功能模 块的自由挂载与调度,具备高速率数据传输、软件 灵活配置的优点,在未增加过多面积和延迟的情况 下,极大地提升了系统的可扩展性。

参考文献:

[1] 刘智. 基于高层次综合的MCU IP核的设计研究[D]. 西 安:西北工业大学,2003.

[2] 白敏丹. 从软件无线电到认知无线电的无线通信发展 现状[J]. 信息通信,2010(1):72-76.

[3] 朱魁. 基于 FPGA 的一种数字下变频设计[D]. 南京:南 京邮电大学,2017. [4] Shankland S,赵嘉. 2021 年 5G 智能手机占全球总销量 15%[J]. 中外管理,2017(12):18.

[5] 李超杰. 基于 AD9364 的小型化弹载遥测系统设计[D]. 太原:中北大学,2022.

[6] 孙金中,付秀兰,高艳丽. 基于软件无线电架构的多模 导航 SoC 芯片设计[J]. 现代电子技术,2022(18):37-40.

[7] 王志军,黄忠凡,申翔,等. 一种高速跳频 MIMO 无 线通信系统设计[J]. 通信技术,2022(6):793-800.

[8] 高玉鑫. 基于 AHB 总线的 DMA 控制器的设计与实现 [D]. 沈阳:辽宁大学,2020.

[9] 卢超. 基于 AMBA 总线的 DMA 控制器的设计[D]. 西 安:西安电子科技大学,2022.

[10] 朱峰,刘威. SoC芯片上AHB总线矩阵的设计及验证[J]. 信息技术,2023,47(3):1-5+12.

售前咨询专员

售前咨询专员