技术分享

了解最新公司动态及行业资讯

利用数字技术实现快速跳频通信

1 引 言

跳频通信作为扩展频谱通信的一种,因其良好的抗干扰性和保密性而广泛应用于军事通 信中。跳频通信系统的一项重要参数是频率的跳变速率,它很大程度上决定了跳频通信系统 抗跟踪式干扰(中继转发干扰)的能力[1],这一点在电子对抗中尤为重要。也正是这个原 因,实用的战术跳频电台跳速一直向更高的速率发展,如美国的联合战术信息分系统JTIDS, 其跳频速率达到3.8万跳/秒。

快速跳频扩展频谱多址通信系统(FFH-SSMA),其优越的性能是以系统的复杂性和实现 难度作为代价来换取的。高速的跳变速率带来一系列待解决的问题,其关键是:(1)具备高速 跳变能力的跳频频率合成器;(2)跳频图案的快速同步和同步的跟踪;同时,现代战争对新一 代的军事通信设备的通信制式的兼容性和灵活性提出了很高的要求。这些问题对传统的以模 拟技术实现的跳频系统提出了挑战。特别是跳频图案的同步问题,在载频高速跳变的情况 下,必须以较复杂的算法才能保证良好的同步与跟踪。由于数字技术的发展,如直接数字频 率合成器(DDS)的出现,高速数字信号处理芯片(DSP)的成熟,使得以数字技术实现高速的跳 频通信系统,从而避开模拟技术所难以逾越的技术难题成为可能。本文讨论了一种用数字技 术实现快速跳频(1.9万跳/秒)通信系统的方案及实际的实验结果,证明了用数字技术实现的 可能性和优越性。

2 快速跳频通信系统的关键数字技术

随着数字技术的发展,原本需在模拟域中处理的问题可以转换至数字域中实时处理。本 方案设计中用到如下两项关键的数字技术。

2.1 直接数字频率合成器(DDS)

在FFH-SS系统中,频率合成器是其核心部件。其跳频数和跳频速率是决定整个跳频通信系统性能的主要参数。FFH-SS系统对频率合成器的要求是:(1)输出频谱要纯;(2)频率切 换速率快;(3)频率达到稳定的时间短。

传统的跳频频率合成器是用模拟技术合成的,分为利用混频分频技术实现的直接式频率 合成器和利用锁相技术实现的间接式频率合成器。由于锁相反馈网络的固有特点,间接式频 率合成器频率跳变速率不高(<5000跳/秒),所以不适合作为快速跳频通信的频率合成器。直 接式频率合成器则有电路复杂、体积大、控制不灵活的缺点,难以在对集成度、可靠性及功 能要求都很高的战术电台中使用。

新一代的直接数字频率合成器(DDS),采用全数字的方式实现频率合成,具备如下特点:

(1)很高的频率跳变速率。DDS利用查表和相位累积运算直接输出所需频率的样点值,因 而能快速地进行频率切换。如ANALOG DEVICES公司的AD9850,可达到23M次/秒的频率切 换速率。

(2)高精度的输出频率控制。如AD9850,采用32bits控制,输出频率分辩率可达0.0291Hz。

(3)高集成度。这是由其采用全数字构成方式决定的。高集成度也就带来高可靠性。

由于具备这些特点,使得DDS成为FFH-SS系统所需频率合成器的良好选择。

2.2 高速数字信号处理(DSP)系统

数字化是通信设备发展的总的趋势。特别是无线通信设备,越来越倾向于在IF部分甚至 直接在RF部分进行高速采样,从而转换到数字域中进行处理,这就是软件无线电的思路。高 速数字信号处理(DSP)技术的日益完善,将原本需在模拟域中处理的问题转到数字域中实时处 理提供了可能。在快速跳频FFH-SS中,引入DSP技术进行数字化处理可以带来一系列用模拟 技术实现所无法达到的优点:

‧可获得优异的性能。DSP可以实时实现各种复杂的算法,特别是各种自适应算法。利 用DSP的这种优点,可以设计出优良的同步和定时跟踪算法,来保证在载频高速跳变的情况 下,跳频图案的快速捕捉和跟踪。同时,跳频系统所需的各种滤波器可转化为在数字域中用 软件实现。这样就大大简化了系统的设计并保证了系统的性能。

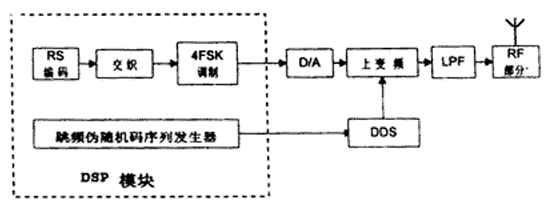

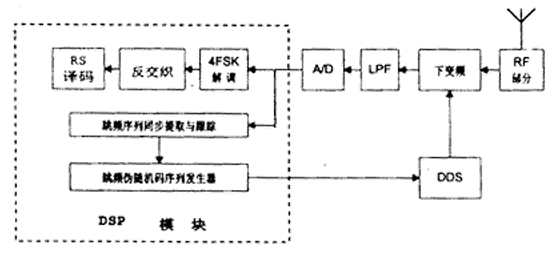

‧高集成度。由系统设计原理框图(图1和图2)可以看到,所有的基带处理,包括RS编码 和译码;交织与反交织;4FSK调制与解调;跳频伪随机码序列的产生;以及跳频图案的同步 与跟踪,均由DSP软件实现。这样就大大简化了整个系统的结构,实现了系统的高集成度, 由此带来体积小、功耗低、高可靠性等优点。

‧高度灵活性。由于整个基带系统都是由软件来实现的,所以具备高度的灵活性和系统 可重构性。无论是FEC码的选择,基带调制制式的选择,还是跳频速率及跳频图案的选择, 都具备良好的可编程性。而这种高度的灵活性正是现代战争对新一代军事通信设备的迫切要求。

3系统设计方案

3.1 系统参数

信息速率:9.6kbit/s

信道速率:12.8kbit/s(75%效率)

FEC码型:RS(31,25)

跳频速率:19200跳/秒

调制制式:非相干4FSK

信道间隔:38.4kHz

跳频序列:Reed Solomon码序列

频点数:2048

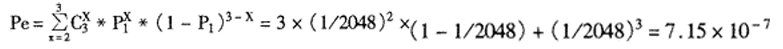

由上述参数可估算出系统的误码性能。采用每个码元3Chips,接收采用3中取2大数判决, 在存在一个单频干扰的情况下,系统的误码率

3.2 系统的原理框图

图1是FFH-SS系统的发送原理框图。所有的基带处理均由一块DSP芯片完成,包括Reed Solomon编码、数据交织、4FSK调制,同时DSP产生跳频伪随机码序列控制DDS产生跳变的载 频,在混频器中与DSP产生的4FSK基带调制信号进行混频,经LPF后,形成IF信号。

图1 快速跳频通信系统发送原理框图

与发送相似,接收系统也是由一块DSP芯片完成所有的基带处理(参见图2)。DSP首先利用 发方发送的同步头来进行跳频伪随机序列的同步,同步以后,DSP控制DDS产生与发方完全同 步的跳变载频,它与收到的跳频信号混频后经LPF获得基带信号,由A/D转换到数字域,再 由DSP完成4FSK解调、反交织和RS译码等处理。在整个解调中,DSP还要进行同步跟踪,以保 证准确的跳频同步。

图2 FHH-SS系统接收原理框图

3.3 器件的选择

DDS选用ANALOG DEVICES公司的AD9850,在120MHz的时钟信号下,能产生分辨率为 0.0291Hz的0至60MHz的频率,并且可以23M次/秒的速率跳变,完全能够满足本设计19200跳 /秒的要求。

DSP则选用TMS320C54,运算速率60MIPS,在每个频率驻留时间52μs内,可执行约3000 条指令,有足够的处理能力完成基带的各个功能模块,满足基带实时处理的要求。

4 结束语

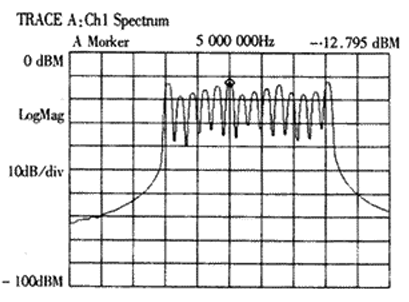

利用本文所讨论的数字技术,已经初步设计成功了一套FFH-SS通信系统。图3为实测的 发送频谱图。实际的设计和实验表明,利用高速DDS和DSP等数字技术实现快速跳频通信是可 行的,能够逾越用传统的模拟实现所遇到的技术难题,并且获得一系列模拟系统所无法达到 的优异性能。如果进一步完善跳频同步算法,最终利用DSP的优异数值处理能力可实现隐蔽 性更好的跳频通信系统。

图3 FFH-SS发送频谱

彭伟军 罗汉文 宋文涛 作者单位:上海交通大学

参考文献

1 查光明,熊贤祚.扩频通信.西安:电子科技大学出版社,1992.

2 Rodger E.Ziemer Roger L.Peterson.Digital Communications and Spread Spectrum System. Macmillan Publishing Company,1985.

3 Analog Devices Inc.AD9850 Data Sheet 1996.

4 Texas Instrument Inc.TMS320C54 User‧s Guide,1996

上一篇:一种实现快速跳频的方法

售前咨询专员

售前咨询专员