技术分享

了解最新公司动态及行业资讯

一种实现快速跳频的方法

频率合成器是电子系统的心脏,是决定电子系统性能的关键设备。随着现代军事、国防及无线通信事业的发 展,移动通信、雷达、制导武器、电子测量仪器和电子对抗等电子系统对频率合成器[1]提出了越来越高的要求。 世界各国都非常重视频率合成器的研究与应用,而锁相频率合成方式由于其合成方式简洁、频谱杂散抑制度好、 硬件简单的特点得以广泛应用。锁相环工作原理是将压控振荡器(Voltage-Controlled Oscillator,VCO)产生的射频 信号与参考信号进行鉴相,通过两信号的相位误差产生直流调谐电压从而锁定压控振荡器。但此种频率合成方式 由于引入了负反馈环路,需要稳态过程,造成最终输出信号跳频速度受到限制。特别在宽带VCO的锁定过程中, 其频率对应的调谐电压范围更大,使得稳态过程时间增加,减缓了频率切换速度,限制了锁相频率合成器在一些 领域的应用,如捷变频雷达、跳频电台等。为了弥补锁相频率合成的这一不足,出现了多种方法加速其跳频速度。 本文介绍了一种提高锁相环跳频速度的方法,在保证输出信号的相位噪声、杂散等性能指标的前提下,实现了对 锁相电路的快速预置,电路稳定可靠,并大大减小了成本、体积,相对原有的方法有一定优势。

1 原理分析

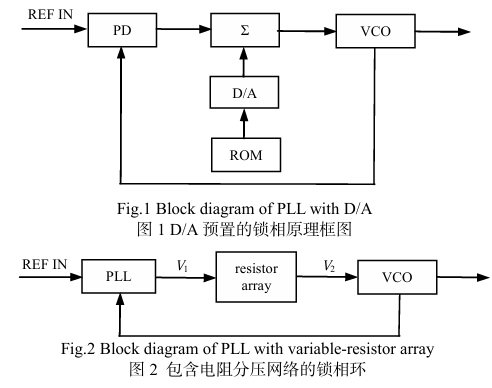

加速锁相电路的跳频速度,其核心通常是加快VCO调谐电压的稳定速度,从而实现VCO输出信号频率的 快速切换。因此,为了进一步缩短锁相环对VCO的锁定时间,往往采用预置技术辅助锁相电路对VCO的控制, 即先产生一调谐电压将VCO快速牵引至所需频率附近,再由锁相电路进行精确锁定,由此大大减小了锁相电路 的捕获范围,增加了锁定速度。 传统的,为了实现预置电压的产生,多采用D/A预置技术[2],即通过对VCO调谐电压的模数转换,将其电 压值以二进制码的形式存贮在ROM中,在工作过程中根据外部频率码提取各电压值的二进制码,并通过D/A合 成预置电压。其原理框图如图1所示。该方法可产生较精确的预置电压,但由于采用了数模转换器件,不可避免地会引入有源数字噪声,恶化VCO输出信号的噪声、杂散性能,同时需要对VCO预先扫频,形成码表,导致 D/A预置电路成本较高,电路较为复杂。

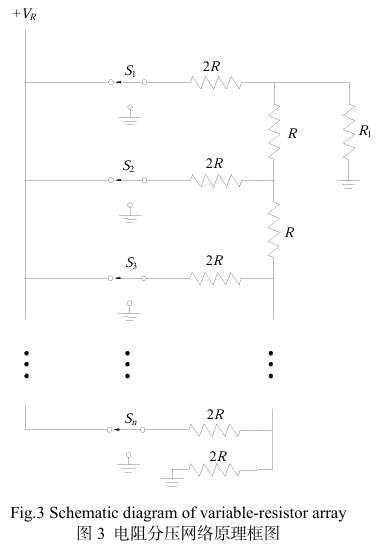

分析锁相环对VCO调谐的原理可以看出,环路中 的基于运放组成的有源积分滤波器产生调谐电压,电压 波动越大则调谐速率越慢,因此缩减调谐电压变化的范 围,尽可能将其限制在最小的区间即可实现对VCO的 快速锁定。基于以上分析,本方案在锁相环与VCO间 增加一组电阻网络[3−6],通过不同电阻值对调谐电压进行 分压,将运放输出的电压稳定在极小的范围内,从而达 到快速跳频的目的。其锁相环组成框图见图2。

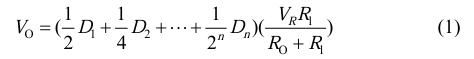

如图2所示,相对传统的锁相环结构,在VCO与 锁相环之间插入了一个电阻分压网络,当锁相环工作时 鉴相器输出电压V1基本不变,VCO调谐电压V2的变化 主要依靠电阻分压网络分压实现,电阻分压网络见图3。

如图3所示,电阻网络包括了电阻及多个电子开关, 通过电子开关的切换,组合形成多种电阻值,在运放输出电压波动量极小的情况下,实现对环路滤波器输出电压 的分压,形成多个调谐电压值,大范围调谐电压完全由电阻网络分压形成,使环路输出的调谐电压快速切换到目 标调谐电压,实现锁相环的快速频率切换[7−8]。

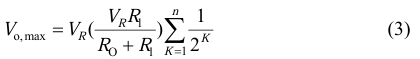

针对图3进行分析,梯形电阻分压网络由电阻2R,R和内

部连接的开关组成。经过计算,当VCO输入端阻抗Rl极大时,

该网络的等效输出电阻RO=R,并且与开关的位置无关。导出

的输出电压表达式为

式中:D表示各个开关的状态;n为所用开关数。当开关Sn接

到+VR时,Dn=1;反之,当Sn接地时,Dn=0。这个网络的分

辨率,即最小输出电压增量是

因此,输出的电压精确度不但取决于参考电压的精确度和

梯形电阻的误差,还与梯形网络的分辨力有关。当D1=D2=…

=Dn=1时,输出电压最大值为

通过以上计算分析可知,为了实现对VCO调谐电压的分 压,应首先确定VCO的最大调谐电压及所用开关的数量,即n。

按照以上分析方法,对某型频综进行改进应用。首先确认所需开关数。在VCO输出频率范围为1 400 MHz~

1 664 MHz时,对应的调谐电压为1.1 V~4.1 V,按照步进频率1 MHz进行预置,则对应的1 MHz步进时电压步

进约为0.011 V,当输出电压为最大值即4.1 V时,对应的电阻开关网络组合量为 ,则可

计算出所需开关数量n>8,可确定开关总数为n=9。假设VCO处于最高频率即电压为4.1 V时,对应的最大开关

码值511,则相应的调谐电压分辨力为0.008 V,小于0.011 V,满足VCO实际调谐电压步进。

,则可

计算出所需开关数量n>8,可确定开关总数为n=9。假设VCO处于最高频率即电压为4.1 V时,对应的最大开关

码值511,则相应的调谐电压分辨力为0.008 V,小于0.011 V,满足VCO实际调谐电压步进。

确认了开关数后,根据VCO给出的调谐曲线,按照不同频率对应的调谐电压值计算出对应的开关状态,即 D值。频综正常工作时,通过预先计算控制各位开关的闭合,组合出不同的调谐电压,迅速锁定VCO。

2 实际测试结果及对比

针对以上分析,在相同跳频状态下,对改进前后的切换时间进行了实测。

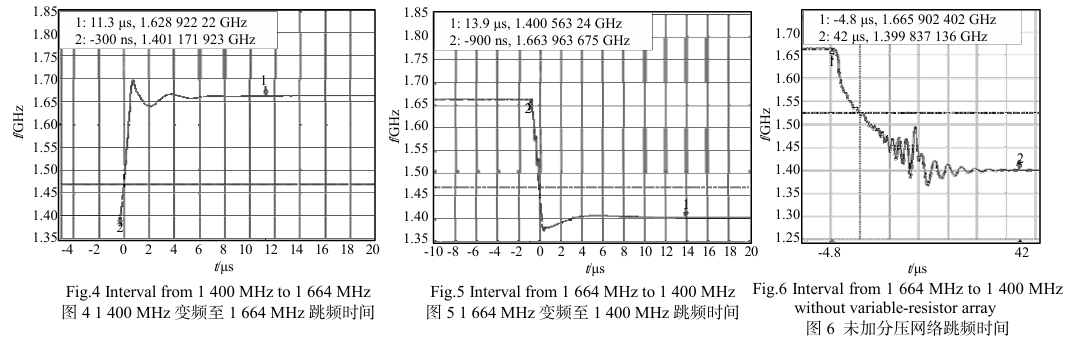

对频综两端点频率1 400 MHz与1 664 MHz两个信号之间进行切换测试,测试仪器为E5052B,实测结果如 图4、图5所示,实测跳频时间在15 μs以内。在其他状态保持不变的情况下,断开电阻开关网络,再次进行测 试,跳频时间实测如图6所示,实测跳频时间为47 μs。

由图4~图6可知,采用电阻开关网络的锁相环的跳频时间相对原普通锁相环减少了70%左右,同时,由于 多为无源器件,没有引入附加噪声,改进前后信号的相位噪声及杂散抑制度无明显恶化。

3 结论

通过以上的分析及对比,可以看出,采用电阻开关网络对锁相环进行预置,在保证相位噪声、杂散等指标不 变的前提下提高了跳频速度,实现方便,成本低,体积小,扩大了锁相频率源产品的应用范围,对系统指标的提 升有较大的推动作用。

万 鸣,魏 萍,王贵昌 (成都西科微波通讯有限公司,四川 成都 610036)

参考文献:

[ 1 ] Evers A F. A Versatile Digital Frequency Synthesize for Use in Mobile Radio Communication Sets[J]. Electronic Engineer, 1966,38(5):296-303. [ 2 ] David F Hoeschele. Analog-to-digital and digital-to-analog conversion techniques[M]. New York:John Wiley, 1994.

[ 3 ] 何松柏. 频率合成器原理与设计[M]. 北京:电子工业出版社, 2008. (HE Songbai. Frequency Synthesizers Theory and Design[M]. Beijing:Electronic Industry Press, 2008.)

[ 4 ] 郑贵强. 锁相环路的宽带调频技术[J]. 信息与电子工程, 2004,2(4):88-91. (ZHENG Guiqiang. Wideband FM Technique with Phase Locked Loops[J]. Information and Electronic Engineering, 2004,2(4):88-91.)

[ 5 ] 胡罗林,杨晓庆,吴洋,等. 不破坏锁相环路稳定性的鉴相泄漏抑制[J]. 信息与电子工程, 2005,3(2):44-46. (HU Luolin, YANG Xiaoqing,WU Yang,et al. Restraint for PD Leakage without Damaging the PLL Stability[J]. Information and Electronic Engineering, 2005,3(2):44-46.)

[ 6 ] 张厥盛. 锁相技术[M]. 西安:西安电子科技大学出版社, 1994. (ZHANG Juesheng. Technology of Phaselock[M]. Xi'an: Xidian University Press, 1994.)

[ 7 ] 费元春. 微波固态频率源理论设计应用[M]. 北京:国防工业出版社, 1994. (FEI Yuanchun. Microwave solid-state frequency source: Theory design application[M]. Beijing:National Defense Industry Press, 1994.)

[ 8 ] Alexander Chenakin. Frequency Synthesizers Concept to Product[M]. Norwood MA:Artech House, 2011.

售前咨询专员

售前咨询专员