技术分享

了解最新公司动态及行业资讯

小型化软件无线电硬件平台关键技术研究

[摘要] 软件无线电硬件平台的发展趋势不仅是追求更多功能和更高性能,而且小型化和轻量化也成为其未来发展的方向。面向机载软件无线电系统,在分析现有架构的基础上,从改进设计架构、增加资源集成度和提高资源利用率三个角度切入,对射频采样、封装系统、片上系统和局部重配置等关键技术进行了研究,并提出对应的设计方法,为构建小型化的软件无线电硬件平台提供了参考。

[关键词] 软件无线电;小型化;采样;封装系统(SIP);片上系统(SOC);局部重配置

Research on Key Technologies of Miniaturized Software Radio Hardware Platform

SHEN Cong,WU Long

(China National Aeronautical Radio Electronics Research Institute, Shanghai 200241, China)

Abstract: The development trend of software radio hardware platform is not only pursuing more functions and higher performance, but also miniaturization and lightweight. Based on the airborne software radio system, this paper analyzes the existing architecture from three aspects of improving design framework, increasing resource integration and improving resource utilization ratio, the key technologies such as RF sampling, SIP, SOC and partial reconfiguration are studied, and put forward the design method of applying these techniques. It provides a reference for the construction of miniaturized software radio hardware platform.

Key words: software defined radio; miniaturization; sampling; system in package(SIP); system on chip(SOC); partial reconfiguration

0 引言

软件无线电硬件平台是采用标准化和模块化的单元模块通过总线网络交联,用软件完成各种工作频段、调制解调类型、数据格式和通信协议的功能,通过在通用硬件平台上加载不同的通信软件来实现不同的通信模式和功能。该平台主要用于解决传统分立式设备只满足单模式通信需求和不同通信系统之间的交互困难等问题,同时提高硬件平台的通用性、可移植性、维修性和可靠性。

当前产品的小型化需求已覆盖了军用产品、航天器件、工业产品甚至民用消费类产品。随着各类武器和机载平台向网络化和信息化的方向发展,如各类小型、超小型平台、空空导弹、小型无人机以及背负式、手持式电台等,对通信容量和组网能力提出了更高的要求。当前采用软件无线电硬件平台实现多种波形功能将需要大量的通信信号信息处理资源,系统的体积、功耗和重量也将随之直线上升,这对机载设备乃至其他武器平台小型化、低功耗和轻量化的需求产生了极大的挑战。

本文基于机载软件无线电平台,从架构设计、资源集成度和资源利用率三个角度入手,在分析当前先进关键技术,包括高性能的模数转换器(ADC:Analog to Digital Converter)应用,封装系统(SIP:System in Package)的封装技术、高性能SOC 的芯片和局部重配置等的基础上,提出了应用的方案,并可拓展应用于其他软件无线电硬件平台,为解决平台小型化的要求提供思路和方法。

1 机载软件无线电硬件平台架构分析

1.1 总体架构

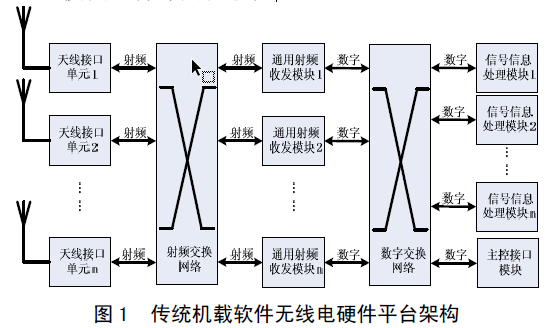

常见的机载软件无线电硬件平台架构如图1 所示。天线接口单元、通用射频收发模块和信号信息处理模块作为通用化和模块化的资源,通过射频交换网络和数字交换网络联接在一起。其中天线接口单元主要用于射频信号大功率功放、滤波和天线选择等;通用射频收发模块用于射频信号的上下变频、滤波和射频信号与数字信号的相互转换;信号信息处理模块完成信号处理算法和信息协议的处理;主控接口模块完成整个平台的管理,包括资源调度、健康维护、信息整合和平台对外接口等。当平台上需要运行的波形数量增加,平台就需要增加通用资源的数量,即增加通用射频收发模块和信号信息模块,从而增加平台体积、功耗和重量。平台小型化的思路应当是将数模转换部分尽量靠近天线,同时在有限的模块体积内尽量增加资源,以及在同样的资源条件下实现更多的功能,从而减少模块的数量和种类。

1.2 射频收发架构

由于受限于放大器和滤波器的性能,特别是ADC 的带宽、采样率,通信系统大多采用二次变频的超外差结构,该架构的优点是稳定性好、灵敏度高,它降低了对器件(特别是ADC)的性能要求,但其最大的缺点在于使用的模拟器件较多,一致性差,模块器件布局面积大。

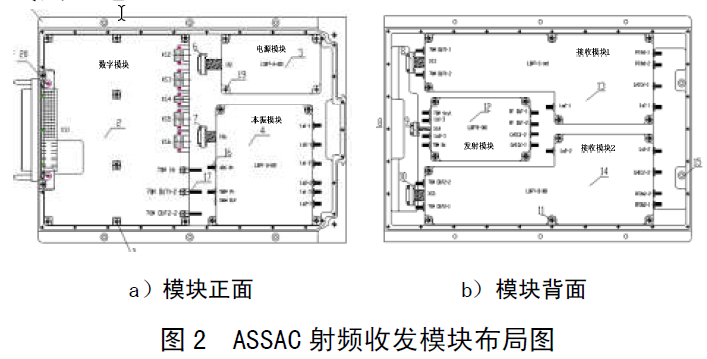

以常用航空电子体系架构标准(ASSAC:AlliedStandardsAvionics Architecture Council)标准模块大小为例,带有二个接收通道和一个发射通道的模块采用二次变频体制的布局图如图2 所示。模块正面有数字模块用于数字控制、信号处理和ADC 和模数转换器(DAC:Digital to Analog Converter)电路,电源模块包括开关电源,以及过压、欠压、过流和浪涌抑制电路,本振模块包括两个跳频源和一个固定点频源,以及开关选通网络等。模块背面有两个射频接收模块和一个发射模块,包括两次混频、滤波放大及开关选通等电路。可见采用二次变频架构的射频收发模块射频部分的面积大约占了整个模块的7 成左右,重量比例也相当。同时,该架构也不符合软件无线电将数字信号处理部分更靠近天线的理念。

1.3 信号信息处理架构

软件无线电硬件平台中的信号处理资源通常由现场可编程门阵列(FPGA:Field Programmable Gate Array)和数字信号处理器(DSP:Digital Signal Processor)构建,FPGA 主要负责完成编码、调制、滤波、同步、解调、解码等处理过程,DSP 善于处理大量浮点数据,完成数据的打包、解包、统计、调度及信道参数的下发等。每个机载通信导航识别(CNI:Communication Navigation Identification)波形一般各需要一个FPGA加上DSP 的信号处理通道完成信号信息处理,雷达根据功能则需要占用8到16 个8 核DSP。

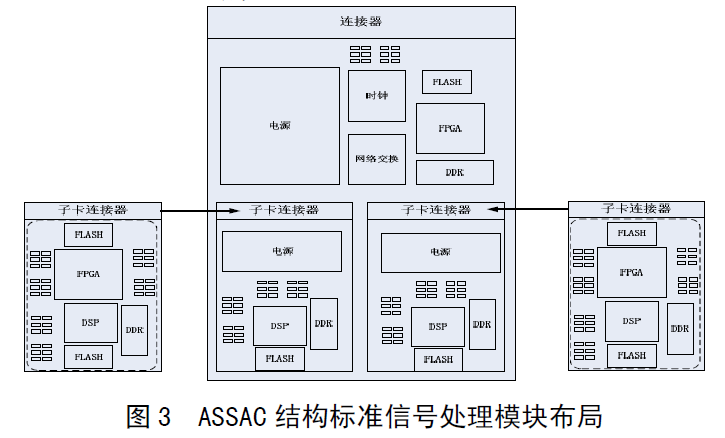

如图3 所示,在符合ASSAC 标准尺寸的模块条件下,采用扣板的设计形式,最多能放下3 个型号为XC7K325T 的FPGA, 以及4 个型号为TMS320C6678 的DSP。

1.4 主控接口架构

机载软件无线电平台中的主控接口模块主要由PowerPC 与FPGA 组合的形式构建。PowerPC 加载嵌入式实时操作系统,负责对整个平台进行管理,而FPGA 因接口丰富,主要用于接收PowerPC的指令和数据,完成对外接口的通信。

以常用PowerPC 型号P2020 以及XC7K325T来说,两个芯片面积较大且外围电路较多,加之机载环境下对外接口丰富,通常包括FC 总线、1553B总线、ARINC 429 总线及RS 422 总线等,器件占用空间需求大,在有限的模块体积下,对设计复杂度、印刷电路板的布局布线造成了压力。

2 射频采样架构设计

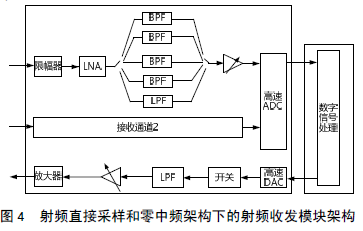

随着高性能ADC 器件的日益成熟,可考虑采用射频直接采样和零中频的方式来简化射频电路的设计,实现射频收发电路的小型化,从而提高灵活性。

射频直接采样是直接对射频信号进行数字化处理,无需进行模拟下变频,通过高带宽和高采样的ADC 将射频信号直接转换为数字信号,由数字处理器进行数字下变频及滤波转换等后续处理。以TI 公司的模数转换器ADC12D1800RF 为例,采样频率最高为3.6 Gbit/s,采样精度为12 位,可只直接对2.7 GHz 的射频信号进行采样,足够覆盖大多数CNI 及雷达波形的工作频段。

零中频则是将接收到的信号直接降至基频,及中频信号为0 Hz,优点是抑制镜频干扰,电路设计简单,只需要一个低噪声放大器,再用混频器经过下变频后通过滤波器,对I 路和Q 路信号进行分流直接进入基带。该特点使其电路可方便做成IC 芯片。以ADI 公司的AD9361 为例,这款面积仅为10 mm×10 mm 的芯片级器件集成双独立通道,具有200 kHz~56 MHz 可调谐带宽,工作频率支持70MHz~6 GHz。内部集成了模拟滤波、混频器、数据转换器、发射和接收通道的频率合成器以及包括可编程增益、直流偏置校准等数字域的其他功能,通过正交误差校准和直流偏置校准的功能优化很好的解决了此前零中频架构的直流偏置和正交误差限制,从而使零中频架构成功应用于软件无线电的芯片产品。

若采用上述射频直接采样和零中频构建射频收发模块架构如图4 所示,射频电路简化为只需要放大器、滤波器、ADC 和DAC 组成,该架构大大降低了模块器件布局面积,减少了模拟器件,提高了一致性,缩短设计开发和调试的周期。初步估计该架构可在ASSAC 模块尺寸条件下实现4 个射频接收和4 个发射通道,即较二次变频体制资源容量提高了一倍。还可以考虑将信号信息处理模块的资源前移到射频收发模块中,这能省去信号信息处理模块,达到减少整体尺寸和重量的目的,满足软件无线电减少模拟环节,数字端更靠近射频前端的要求。

3 资源集成技术

要在同样的模块体积下集成更多的资源、减少对模块数量的需求,目前主要通过SOC 芯片技术和SIP 芯片封装技术实现。SOC 芯片技术遵循摩尔定律,在同样大小的芯片中集成更多的晶体管,从而实现更丰富的功能,主流的SOC 芯片主要包括Xilinx 的ZYNQ-7000 系列芯片和RFSoC 芯片,而SIP 是从封装角度出发,将多个芯片和器件的裸片封装在一起。

3.1 SOC 芯片

3.1.1 ZYNQ-7000 系列

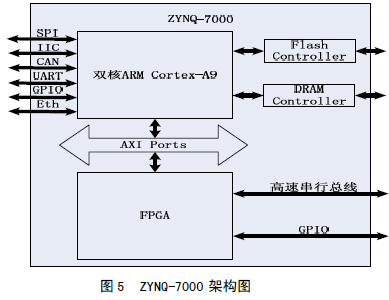

Zynq-7000 是Xilinx 全可编程、可扩展的处理平台结构,如图5 所示,该结构在单芯片内集成了基于双核ARM Cortex-A9 多核处理器的处理系统(PS :Processing System)和Xilinx 可编程逻辑(PL :Programmable Logic),它包含片上存储器、外部存储器接口和一套丰富的I/O 外设。

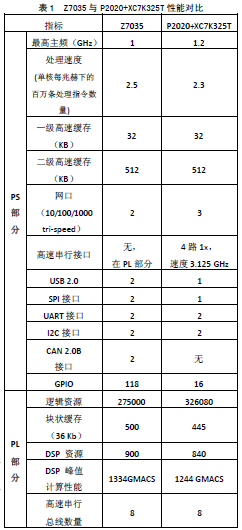

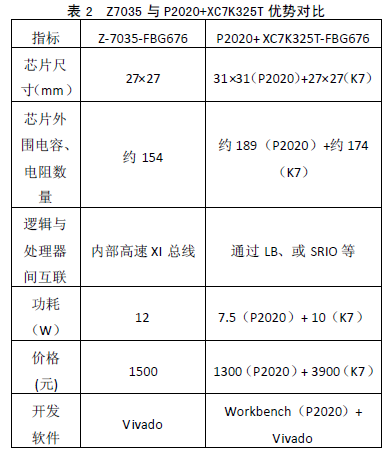

Zynq-7000 系列芯片非常适合替代主控接口模块中的PowerPC 与FPGA 组合,其中PS 部分可完成P2020 的工作,PL 部分与K7 系列FPGA 相当。以Z7035 为例,它与PowerPC 和FPGA 组合的性能对比如表1 所示。可见Zynq-7000 的PS 部分与P2020 性能基本相近,甚至部分指标优于P2020。PL 部分也与XC7K325T 性能相近。

若采用Z7035 芯片替换PowerPC 与FPGA 的组合,功能、性能和接口上没有降低和减少,但在布板面积、器件数量、功耗和设计开发上都会有一定优势,对比如表2 所示。可见采用Z7035 芯片优势如下:

(1)芯片及模块器件布局面积大大减小,外围电容、电阻数量减少约一半;

(2)P2020 与K7 间互联需要外部总线,需要考虑布线信号完整性和走线等问题,而ZYNQ 芯片内部PL 与PS 之间内部通过千兆级低功耗的AXI总线互联,使用方便;

(3)功耗降低约1/3;

(4)成本降低约2/3;

(5)开发软件只需要用Vivado 即可完成PL和PS 两部分软件与逻辑协同开发,高效快捷。

3.1.2 RFSoC

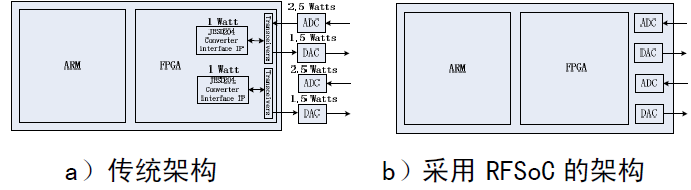

Xilinx 公司推出一种采用射频(RF)级模拟技术的全可编程(All Programmable)RFSoC,它将高性能ADC 和DAC 集成到SOC 中。RFSoC 将RF 数据转换器以及高性能16 nm UltraScale 加上可编程逻辑和ARM 多处理系统集成在一起,形成了一个全面的模数信号链,它主要包括:8 个4GSPS或16 个2GSPS 12 位ADC、8-16 个6.4GSPS 14 位DAC、四核Cortex-A53 和双核Cortex-R5、16 nmUltraScale 加上可编程逻辑、多达930,000 个逻辑单元和超过4,200 个DSP Slice。

传统的无线电系统包含一个处理器、可配置逻辑、连接IP,以及数据转换器。在高RF 频率下工作时,典型的单通道ADC 的功耗约为2.5 W,DAC 的功耗约1.5W,JESD204B 协议的接口功耗约1 W。采用RFSoC 集成减少组件后,能降低功耗和封装尺寸。在典型4 路发送、4 路接收(4Tx/4Rx)的天线配置中采用RFSoC 的实现方法比分立实现方法功耗降低41%,模块器件布局面积节省约50%。

此外,采用RFSoC 集成还可省去JESD204B IP核和串行收发器,分立式器件之间的连接速率随着带宽的扩展也越来越高,大多数高采样率的ADC都使用基于JESD204B 协议的速率高达12.5Gbit/s 的高速串行接口,JESD204B IP 核会消耗大量的功耗,同时高速下的信号失真也需要耗费大量的时间和精力做调试。

3.2 SIP 技术

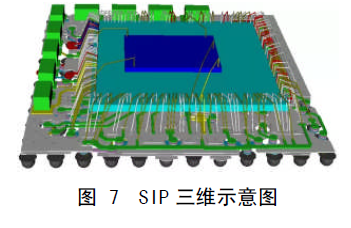

SIP 封装是将多种功能芯片,包括处理器、存储器等功能芯片以及电阻器、电容和电感器等无源器件集成在一个封装内,从而形成一个系统或者子系统。如图7 所示,SIP 是对不同芯片进行并排或叠加的封装方式,将多个具有不同功能的有源电子元件与无源器件,包括微处理器、存储器( 如EPROM 和DRAM)、FPGA、DSP、电阻器、电容和电感器,通过高密度互联基板和高密度互联设计组装到一起,实现一定功能的单个标准封装件。将原本各自独立的封装元件改成以SIP 技术整合,既能缩小封装体积以节省空间,并缩短元件间的连接线路而使电阻降低,提升电性效果,最终呈现微小封装体取代大片电路载板的优势,又可维持个别晶片的原有功能。

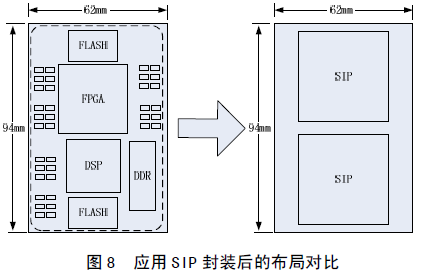

信号处理一般多用FPGA+DSP 的组合形式完成,以XC7K325T 加上TMS320C6678 的组合为例,可将FPGA 和DSP 以及外围存储芯片、电阻器、电容和电感器通过SIP 技术封装成一颗芯片。如图8所示,在一个94 mm×62 mm的子卡PCB 上,原本只能放置一片XC7K325T 和一片TMS320C6678,及其存储芯片和电阻器、电容和电感器等无源器件,将其通过SIP 技术封装成一个芯片,面积约为40 mm×40 mm,可以在同样的PCB 上放置两片封装后的芯片,即在同样面积的PCB 上资源量增加了一倍。因此在系统需要同样资源量的情况下,对信号处理模块的数量需求将降低一半。

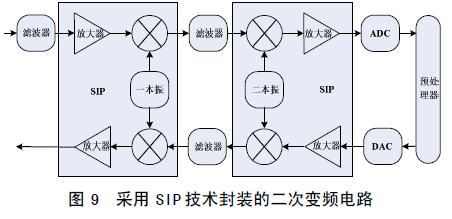

同时,在射频收发电路上,若采用二次变频体制,也可以通过SIP 技术封装除带通滤波器外的混频、本振、放大器和衰减器等,如图9 所示,目前带通滤波器的Q 值性能和可靠性不高,暂不考虑集成。通过集成也可大大缩减中发射、接收和本振电路的模块器件布局面积。

4 资源复用调度技术

软件无线电平台要在通用硬件上运行不同应用软件,需采用动态重构技术完成系统在通电运行过程中的应用切换。动态重构分为全局重配置和局部重配置两种,全局重配置对整个芯片程序进行重新配置,该方式会导致部分应用功能暂停工作一段时间,大大降低了系统的整体性能。最重要的是,该重构方式限制了每个芯片只能同时实现一个应用功能,资源利用率较低,而目前主流FPGA 和DSP 的资源完全可以同时实现多个CNI 波形。由于FPGA 能实现局部重配置,而DSP 不具备该功能,因此为提高资源利用率,可在FPGA 上采用动态局部重配置技术,在DSP 上采用多核多任务并行调度技术。

4.1 FPGA局部重配置技术

FPGA 的局部重配置功能,一方面,允许对FPGA 指定区域使用新的功能进行重配置;另一方面,允许在器件的剩余空间继续运行当前的设计。FPGA 局部重配置将各种应用通过子模块实现,将可重配置的子模块需要的逻辑资源在FPGA 上规划好,在系统运行时根据需求下载相应的子模块程序至FPGA,而其他子模块的应用在其他应用加载时不受影响。

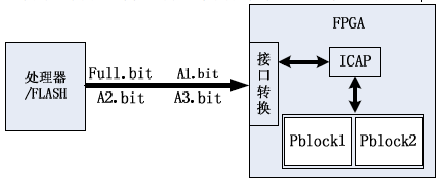

如图10 所示,FPGA 内的逻辑分割成两种不同的类型:可重配置的逻辑和静态的逻辑。FPGA 块内灰颜色的区域标示静态逻辑,Pblock1 和Pblock2为可重配置逻辑。静态逻辑所保留的功能不会因加载一个部分比特文件就受到影响。可重配置逻辑通过替换部分比特文件的内容来改变自身的功能。

局部重配置首先要生成全功能的bit 文件和各个子应用的bit 文件。全功能的bit 文件即为程序的顶层,主要完成各个子应用的模块声明,并在FPGA中划分好子应用占用的逻辑区域(Pblock),分配资源。子应用则将子模块逻辑填入顶层划分好的资源区域中,采用独立编译的模式生成网表,并最终得到bit 文件。在工作时,首先要通过第三方处理器或者FLASH 存储器加载全功能的bit 文件,再根据需要加载子应用的bit 程序。被加载的FPGA 由内部配置接口(ICAP:Internal Configuration Access Port)实现FPGA 内部selectmap 模式加载。在加载某个子应用的同时,其他诸如接口通信之类的子应用及静态逻辑不受影响,从而极大提高了软件无线电系统的性能。

4.2 DSP 多核多任务并行调度技术

目前DSP 只能完成全局重配置,但无局部重配置的功能。随着以TMS320C6678 为代表的多核DSP的成熟应用,可以考虑在一个DSP 内采用多核并行处理多任务的方式来完成多波形功能,从而提高DSP 的资源利用率。目前TMS320C6678 的单核足够圆满完成CNI 中的任何波形的算法处理,只有雷达需要多核并行处理,因此可以采用每个核单独处理一个波形算法,以根据任务环境需求调度波形的方式来实现资源的充分利用。

DSP 多核多任务并行调度主要难点有:

1)多功能开发加载方式;

2)各个核功能及其占用内存的划分;

3)核间通信的方式。

(1)多波形开发和加载

DSP 每个核各自运行独立的用户程序,这些程序通常需要单独开发,随即生成多个.out 文件。需要加载多个.out 文件时,通常将其分段放在存储器中,通过core0 一级引导程序来将8 个核的程序搬移到指定位置,并唤醒其余的7 个核跳转至各自的地址处开始执行程序。采用该方式加载程序耗费时间为20~35 s,对实时性要求较高的系统或平台不适用。实时性要求较高的系统或平台可考虑在设计好各个核任务调度和内存分配、映射的基础上,将各独立的任务编写成.lib 文件,以库文件的形式将所有功能任务编译为一个.out 文件正常加载,只需分配好各个核执行相应的任务即可,可以大大缩短加载程序的时间。

(2)多核功能和内存分配

TMS320C6678 中集成了8 个核,每个核都可以独立运行操作系统和应用。多核模式主要分为三类:主从模式、数据流模式和OpenMP 模式。其中数据流模式采用流水式处理数据,即每个核负责处理一个步骤,然后将处理结果传递到下一个核进行后续处理;OpenMP 模式是多核并行处理同一个波形的数据;主从模式以一个核作为主控,其他核只负责执行分配的任务,集中控制分布执行。主核负责调度分配任务,对外收发数据,对内将数据分发给从核,从核独立完成各自的任务。显然采用主从模式符合多波形并行的需求,有利于充分利用多核资源。在TMS320C6678 中,可采用core0 作为主核,其余core1~7 作为从核。

TMS320C6678 的片上根据读写速率将存储资源分为以下几种:一级程序存储空间(L1 Program Memory,简称L1P)、一级数据存储空间(L1 Data Memory,简称L1D)、512 KB 的二级存储空间(L2 Memory,简称L2),以及其他共享空间以及外设存储器,如DDR 之类。一般情况下,为了提高程序运行效率,将读写速率最快的L1P 和L1D 全部配置为高速缓存(Cache),L2 根据程序大小分配RAM和Cache 的关系。对不经常访问或者访问具有随机性的代码和数据, 分配到不被Cache 的内存空间中,降低对Cache 性能的影响和对片上资源的占用。

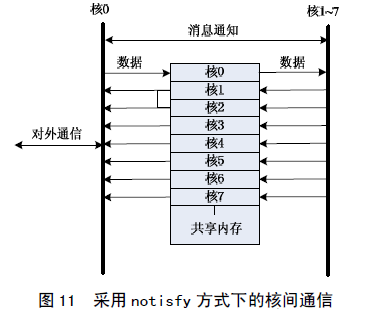

(3)核间通信

TMS320C6678 中的8 个核间较为常用的通信方式有两种,一种是消息通知方式(Notify),另一种是消息队列方式(MessageQ)。

MessageQ 的工作原理是核首先在核间通信共享内存上创建一个共享内存堆,接着每个核将当前核的消息队列与共享内存堆进行绑定并创建接收消息队列和发送消息队列,创建完成后即可相互通信。如图11 所示,Notify 是将数据写入相应的内存地址后,通过通知的方式告知接收方数据的位置,由接收方直接去相应内存地址完成数据读取。MessageQ 的优势是可以直接发送大量数据,但会频繁占用处理器资源,效率较低,因此核间通信推荐采用Notify 的方式。

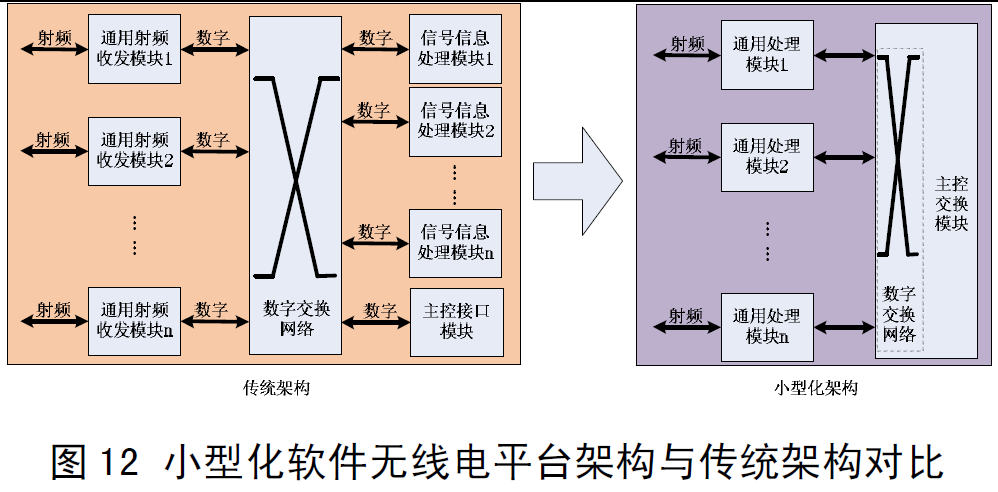

5 小型化机载软件无线电硬件平台架构

采用上述小型化关键技术后的架构如图12 所示,与传统平台架构相比,可将射频收发模块与信号处理模块合二为一,且通过资源集成和复用调度单模块的信号处理资源和能容纳的波形应用也更多。通过SOC 技术集成的主控模块可将原来需要独立模块实现的数字交换网络进行融合。该小型化架构减少了模块种类和交联关系的复杂度,在体积、重量减少的同时,还提高了系统的可靠性和维护性。

6 结束语

在对现有加载软件无线电硬件平台架构进行分析的基础上,提出了现有架构下进行小型化设计的关键点和思路。从改进射频采样架构、增加资源集成度和提高资源利用率三个方向提出了小型化的设计方案,并对小型化设计后的方案与原方案进行对比分析,表明了采用多种关键技术后的收益,进而为软件无线电硬件平台乃至综合射频系统的小型化设计和提供了参考,具有一定的工程应用价值。

参考文献

[1] 徐江海. 小型化低功耗数字信号处理器设计[J]. 智能处理与应用, 2012(4): 71-73.

[2] 胡志东. L 波段射频直接采样数字接收机设计技术[J]. 信息通信, 2015(12): 53-55.

[3] 周建民. 小型化低功耗SIP 封装技术[J]. 集成电路应用, 2014(7): 36-38.

[4] 李飞平. 基于TMS320C6678 的多核程序加载研究与实现[J]. 电子技术应用, 2015, 41(3):31-34.

沈聪,武龙 (中国航空无线电电子研究所,上海200241)

[作者简介]

沈聪(1986—),男,工程师。研究方向:软件无线电平台硬件设计。

武龙(1989—),男,工程师。研究方向:逻辑设计。

售前咨询专员

售前咨询专员