技术分享

了解最新公司动态及行业资讯

基于RFSoC的小型化侦察干扰系统实现

摘要:随着电子技术的发展,雷达侦察干扰设备也得到飞速发展,雷达侦察干扰设备小型化一直是一个重要研究方向。该文以Xilinx公司生产的RFSoC芯片为核心设计了一款小型化雷达侦察干扰系统。该系统能够根据接收到的雷达信号生成脉冲描述字,实时生成各种欺骗干扰信号和压制干扰信号。该设备重量同比基于ADC+DAC+FPGA+DSP 的架构设计的系统重量降低了5 kg,功耗降低了30 W。对该系统的功能进行实验室测试和外场测试,测试结果表明,该系统能够实时侦察接收雷达信号并可发射各种样式欺骗干扰信号和压制干扰信号,使得真实目标很难被雷达识别。

关键词:脉冲描述字;欺骗干扰;压制干扰;侦察接收

Implementation of miniaturized reconnaissance and jamming system based on RFSoC

SHI Lang,ZHANG Ruian,ZHANG Bin

(Xi’an Junlan Technology Co.,Ltd.,Xi’an 710199,China)

Abstract: With the development of electronic technology,radar reconnaissance and interference equipment has also made rapid progress,but miniaturization of radar reconnaissance and jamming equipment has always been an important research direction. A miniaturized radar reconnaissance and interference system is designed based on Xilinx’s RFSoC chip. The system can generate pulse description words based on the received radar signals,and generate various deception and suppression interferences in real time. The weight of the device is reduced by 5 kg compared to the system designed based on ADC+DAC+FPGA+DSP architecture,and the power consumption is reduced by 30 W. Laboratory and field tests were conducted on the functions implemented by the system,and the test results showed that the system can detect the received radar signals in real time and emit various deceptive and suppressive interference signals,making it difficult for the radar to recognize the real target.

Keywords: PDW;deception interference;suppression interference;reconnaissance reception

雷达对抗是侦察、压制敌方电磁频谱的使用并增强我方电磁频谱使用有效性的作战行为,主要包括雷达侦察、雷达干扰和雷达防护等[1]。传统雷达侦察干扰系统核心处理板采用ADC +DAC+FPGA+DSP的架构,体积和功耗都较大,且ADC和DAC与FPGA分开设计需要高速接口才能在器件之间进行通信[2-5]。大部分高速接口采用JESD204B高速串行接口,但是JESD204B的延迟太大,在延时要求较高的场景下不能满足系统要求。现代电子战机载、弹载等应用场景越来越多,传统的实现方法很难满足这些要求。而RFSoC 芯片集成了高速ADC 和高速DAC、ARMCortex-A53 处理器及丰富的逻辑资源,具有尺寸小、功耗低的特性。该文以Xilinx 公司的RFSoC 芯片UltraScale+ RFSoC ZU27DR-1156 为核心,设计了一款小型化雷达侦察干扰系统,能够快速准确地侦察雷达信号,释放各种压制干扰及欺骗干扰等干扰样式[6-9]。验证了雷达侦察干扰系统在此架构的可行性、实现了侦察干扰一体化设计。

1 系统方案设计

1.1 系统硬件设计

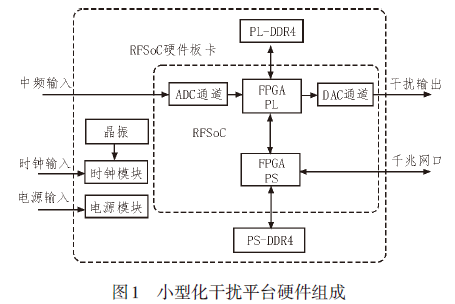

小型化侦察干扰系统由RFSoC 芯片、DDR4、时钟管理模块、电源管理模块及相关接口连接器组成。组成框图如图1所示。

该系统采用模块化的设计方式进行设计,PL侧搭载2 GB、32 bit、3 200 MT/s 的DDR4 用于大脉宽、大带宽干扰信号存储转发,PS 侧搭载4 GB、64 bit、3 200 MT/s的DDR4用于干扰策略计算,ARM侧通过PHY 芯片88E1111 实现千兆以太网接口,满足系统和上位机通信要求,由于PS 和PL 交互的数据量不大,二者之间的数据通信采用BRAM。另外在时钟设计时,考虑了单板调试和系统调试的需求设置了内时钟参考和外时钟参考。

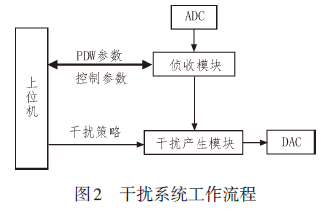

1.2 系统总体工作流程

系统接收射频前端输入的1.3~2.3 GHz 的中频脉冲信号,侦收模块完成中频脉冲信号的采集、频率测量、带宽测量、脉冲参数测量(脉冲宽度、脉冲重复周期和到达时间)以及脉冲样本数据的提取等,同时PDW 的侦察结果通过千兆网口传输至主控上位机。系统工作时先对时钟芯片、ADC配置参数、DAC配置参数进行正确的配置,可使ADC模块和DAC模块能在2.4 GS/s的采样率下稳定工作;在上位机参数的控制下,干扰产生模块通过对侦收模块输出样本数据从距离、多普勒和幅度进行相关调制从而产生密集假目标、随机假目标、切片复制、间歇采样切片等各种干扰信号,最后由DAC 以1.8 GHz 中心频率输出。干扰系统工作流程如图2所示。

2 系统功能实现

2.1 侦收模块

侦收模块需要完成脉冲信号特征参数的测量,形成PDW,并将检测结果上报至上位机,同时还需将收到的雷达信号样本输出至干扰产生模块。ADC实采样信号先经过串并转换将2.4 GHz 的采样信号转换成八路300 MHz 的信号,经过数字下变频模块把信号转换成四路零中频复信号。然后利用Xilinx的CordicIP 完成信号的相位和幅度计算,最后用一阶相位差分法计算信号频率。信号的频率与时钟频率的对应关系如式(1)所示:

式中,Δω 为相位差,Fs 为采样频率,为了提高测频准确度,系统采用四点平均的方法求当前点的频率:采用寄存器对计算出的结果做四级流水,求取平均值即可求得当前的频率。

脉冲宽度、脉冲重复周期以及带宽的求取均依赖于幅度信号,而幅度信息测频时已经获取。脉冲包络信号一般来源于对信号幅度检波或者模拟器件耦合输出的检波信号。系统测量时根据信号的幅度信息求得脉冲包络信号:设置一个动态门限,当信号幅度连续8个点的值大于设置的门限时拉高包络信号,当连续8 个信号幅度低于设置的门限时拉低包络信号,设置合理的检波门限就能够准确提取出信号脉冲包络信号[10-15]。生成脉冲包络信号后,利用包络信号和计数器可计算信号的脉冲宽度和到达时间。当包络信号为高电平时,求得持续时间内信号的最大频率和最小频率,二者相减即可求得信号带宽。最后把测试结果打包通过网口输出至上位机。

2.2 压制干扰

雷达通过对目标回波信号进行检测与跟踪发现目标的存在,并测量目标的各类距离、速度和方位等信息,而对雷达进行干扰的目的就是破坏或阻碍雷达发现、跟踪目标以及测量目标参数。压制干扰正是利用噪声或者类似噪声的信号压制或淹没目标回波信号,阻止雷达正常检测和跟踪目标。任何雷达都存在外部噪声和内部噪声,雷达对目标信息的检测和跟踪都是在这些噪声环境中进行的,而其检测又基于一定的概率准则。一般来说,若目标信号的能量S 与噪声的能量N 的比值(即信噪比S/N )超过一定的目标检测门限D ,则可以保证在一定的虚警概率P fa 下,雷达达到一定的检测概率Pd 。达到检测概率称为可发现目标,否则就称为不可发现目标。压制干扰正是利用强干扰噪声进入雷达接收机,使信噪比尽可能降低,以达到阻碍雷达对目标的检测和跟踪的目的。

2.2.1 压制干扰原理

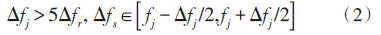

压制干扰主要是通过发射大功率噪声实现的,它能够干扰任何类型的雷达信号。连续噪声干扰一般满足式(2):

其中,Δfr 表示雷达接收机带宽,Δfs 为雷达接收机中心频率,干扰信号中心频率fj 与带宽Δfj 可根据系统引导加以设置。

由于干扰信号带宽Δfj 较宽,一方面对频率引导的精度要求比较低,降低频率引导设备的复杂性;另一方面也能够同时干扰频率分集雷达、频率捷变雷达和多部不同工作频率的雷达。

2.2.2 压制干扰实现

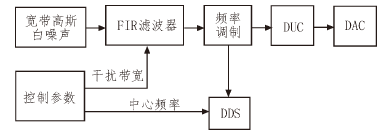

压制干扰实现框图如图3 所示。FPGA 产生宽带高斯白噪声,通过FIR 滤波器组合成所需的干扰带宽,在复数域进行频率调制,然后进行DUC 变换,通过DAC输出至后级模块[16]。

图3 压制干扰实现框图

2.3 欺骗干扰

在电子对抗领域中,欺骗干扰是一种有效的电子攻击手段,它是通过发射假目标信号欺骗敌方雷达,以隐蔽真实数据的电子干扰。欺骗干扰可以使敌方雷达无法从众多的假目标回波信号中识别真实目标,甚至可以使接收通道和数据处理模块过载或饱和。下文以密集假目标为例展开论述。

2.3.1 欺骗干扰原理

密集假目标的实现原理是通过对接收到的雷达信号进行多次延迟叠加和多普勒调制,在某个距离段产生大量的假目标,从而可以抬高CFAR 的参考单元电平,降低和压制雷达对真实目标的检测概率从而对雷达形成距离欺骗和角度欺骗的双重干扰效果[17-18]。以下以距离干扰为例进行分析。

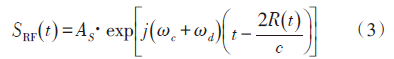

根据目标回波信号模型,且不考虑雷达载频捷变和线性调频等因素,在雷达接收机接收到的目标回波信号形式为:

要使假目标在距离维有干扰效果时,单个假目标形式应该为:

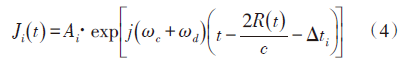

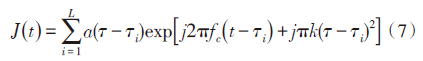

式中,AS 为雷达信号的幅度、Ai 为第i 个假目标信号的幅度,且Ai >As ;ωc 为雷达信号的载频,ωd为雷达信号的多普勒频移;R(t) 为真实目标与雷达之间的距离;Δti 为第i 个假目标的延迟时间;c 为光速,即c =3×108 m/s 。则假目标干扰信号形式为:

其中,L 为复制脉冲个数,Ai 为干扰信号强度,τi 为第i 个复制样本时延,不同时延分布代表不同复制方法。

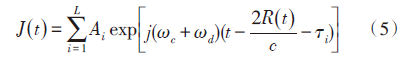

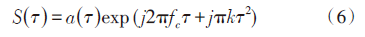

假设雷达发射信号为线性调频信号,表达式为:

干扰信号是经过延时累加的结果,其表达式为:

其中,τi 为第i 次复制时的延迟时间,L 为假目标复制个数。

通过延迟叠加方法产生的脉内多假目标,既能够保证干扰信号同雷达发射信号之间的相关性又保证了所产生的干扰在距离维不仅仅只是一个峰值的点目标,而是不同距离段的密集假目标,从而使得雷达很难区分真假目标。

2.3.2 欺骗干扰实现

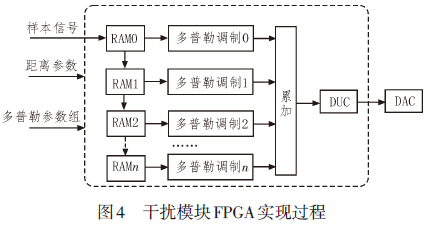

干扰产生模块通过对接收的样本信号进行距离调制、幅度调制和多普勒调制产生欺骗干扰信号,经DUC模块输出至DAC模块,FPGA实现过程如图4所示。双口RAM 主要实现距离欺骗,多普勒调制模块主要实现速度欺骗。该系统可根据不同参数配置,实现密集假目标干扰、切片干扰、多普勒干扰和各种压制干扰等干扰样式。

3 系统测试分析

在完成侦收模块及干扰产生模块的FPGA 程序设计完成后,在实验室环境下,用信号源模拟雷达,产生脉冲信号,侦察干扰系统接收雷达信号测试PDW、释放干扰。测试了板卡的功耗为40 W,比传统的系统降低了30 W。

3.1 PDW 测试

设置信号源频率参数范围为1 300~2 300 MHz,功率范围为-30~+5 dBm;脉冲宽度范围为0.5 μs~2 ms;重复周期范围为0.5~10 ms。

测试结果:频率误差在-0.5~0.5 MHz以内;脉冲宽度误差在-1~1 μs以内。

测试结果能够满足干扰引导和后续分选功能对PDW精度的需求。

3.2 干扰测试

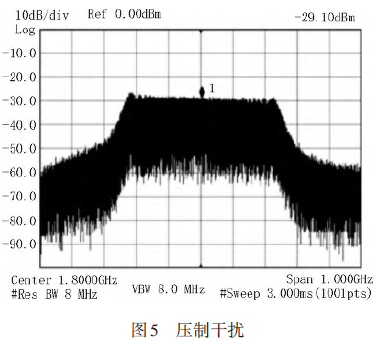

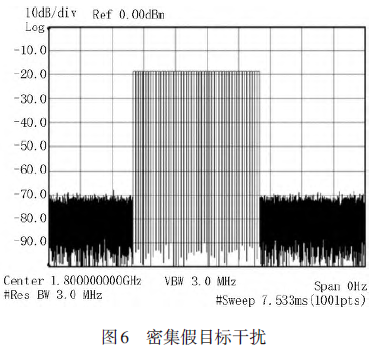

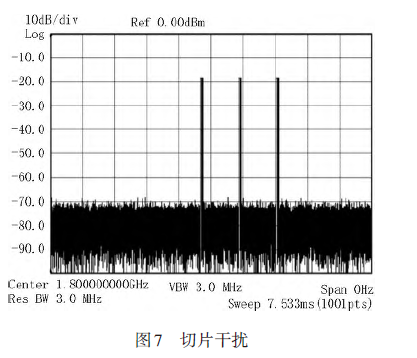

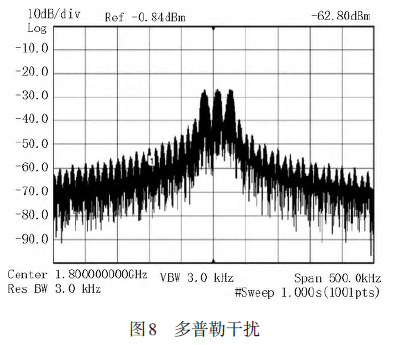

该文设计的侦察干扰系统可产压制干扰和欺骗干扰。室内测试时,将信号源输出和侦察干扰系统输入连接起来,侦察干扰系统的输出接至频谱仪。在显控终端设置干扰参数,再在频谱仪上观察干扰信号频谱,结果如图5-8所示。

图5 是中频频率为1.8 GHz、带宽为500 MHz 的噪声干扰频域图,图6 是脉冲宽度为10 μs,周期为5 ms的40 个假目标干扰时域图,图7 是脉冲宽度为200 μs,切片宽度为10 μs的切片干扰时域图,图8是中心频率为1.8 GHz,3 个多普勒频点的多普勒干扰频谱图。

外场试验时,针对某警戒雷达开展实验。设备安装在无人机上,无人机在距离雷达200 m,高度80 m高度悬停。设备接收某雷达的主瓣信号并释放干扰。系统产生的各个干扰样式均能使得雷达不能及时、准确地发现真实目标[19-20]。目前,所设计系统在某干扰模拟训练装备上完成试用,准备交付。

4 结论

该文针对机载、弹载等应用场景,在传统侦察干扰机系统的基础上,利用RFSoC 芯片设计一款小型化侦察干扰系统。介绍了欺骗干扰和压制干扰的产生原理并对PDW 测量、压制干扰和欺骗干扰进行了实验室验证和外场验证。测试结果表明该小型化侦察干扰系统具有较好的效果,可很好的实现雷达信号侦察干扰功能,相较于传统的侦察干扰机在重量、尺寸和功耗上由明显的改善,能够很好应用于机载、弹载等应用场景。

师浪,张瑞安,张宾(西安君兰科技有限公司,陕西西安710199)

参考文献:

[1] 赵国庆.雷达对抗原理[M].2版.西安:西安电子科技大学出版社,2012.

[2] 杨昕橙.雷达有源干扰通用平台设计与实现[D].哈尔滨:哈尔滨工程大学,2019.

[3] 陈通.基于信道化的雷达侦察与干扰技术研究与实现[D].哈尔滨:哈尔滨工程大学,2020.

[4] 刘保阔.基于FPGA的电子侦察及有源干扰生成技术研究[D].西安:西安电子科技大学,2022.

[5] 刘俊杰.基于ADRV9009的雷达侦察干扰平台设计[D].西安:西安电子科技大学,2022.

[6] 张玉芳.基于DRFM的雷达干扰技术研究[D].西安:西安电子科技大学,2005.

[7] 张恒,张文旭,陆满君,等.基于DRFM的间歇采样延时叠加干扰生成设计[J].制导与引信,2020,41(3):25-29,40.

[8] 周显歆,汪飞,窦山岳.基于DRFM转发信号的干扰加探测性能分析[J].航天电子对抗,2023,39(6):41-50.

[9] 刘百玲.超宽带数字侦察接收机中瞬时测频的设计与实现[D].北京:北京理工大学,2016.

[10]吴民杰.宽带干扰模拟器侦察分系统设计与实现[D].成都:电子科技大学,2021.

[11]罗勇江,杨腾飞.基于AD9361的雷达干扰信号模拟器设计[J].实验技术与管理,2020,37(7):105-109.

[12]费曰振,谷加臣,郭辉,等.相参压制干扰对雷达旁瓣对消性能的影响分析[J].航天电子对抗,2023,39(6):51-55.

[13]刘俊杰,郑沛,赵忠凯.基于ADRV9009 的小型化雷达侦察干扰实现[J].电子信息对抗技术,2022,37(5):14-18,23.

[14]罗加钰.大带宽数字信道化雷达侦察干扰技术研究与实现[D].哈尔滨:哈尔滨工程大学,2023.

[15]陈通,赵忠凯.基于数字信道化的雷达侦察与干扰系统设计[J].电子信息对抗技术,2020,35(4):5-8,52.

[16]李宝鹏,彭志刚,王艳军,等.基于VST-FPGA的雷达侦察与干扰系统设计[J].电子测量与仪器学报,2020,34(11):181-187.

[17]刘建林.雷达/通信电子战系统一体化及效能评估方法[J].航天电子对抗,2022,38(4):20-25.

[18]王守权,高伟亮,李宝鹏,等.一种多功能雷达干扰信号发生设备[J].兵器装备工程学报,2021,42(1):44-49.

[19]王明君.基于数字信道化的侦察干扰一体化技术[J].舰船电子对抗,2018,41(3):1-5,41.

[20]周红平,王子伟,郭忠义.雷达有源干扰识别算法综述[J].数据采集与处理,2022,37(1):1-20.

售前咨询专员

售前咨询专员