技术分享

了解最新公司动态及行业资讯

基于软件无线电架构的通信干扰模拟设备

顾 杰, 林加涛, 张明利, 王 勇 (上海无线电设备研究所,上海 201109)

摘 要:针对电子对抗环境下通信设备的抗干扰性能测试评估需求,设计并实现了一种基 于软件无线电架构的通信干扰信号模拟设备。介绍了系统的总体方案和干扰模拟处理流程, 并详细描述了干扰产生模块的构成,包括任意波形产生单元等硬件和干扰样式生成等软件算 法。测试结果表明:干扰频率、带宽、波形特性等各项技术指标满足通信设备抗干扰性能测试 需求,且具有软件可重构、功能可升级的特点,可满足模拟新类型的通信干扰信号等需求。

关键词:干扰模拟;软件无线电;现场可编程逻辑门阵列;电子战

0 引言

在电子战环境[1]下,战场存在大量通信设备、 雷达探测设备、干扰设备等,它们辐射出大功率、 宽频谱电磁信号,以及针对性极强的各类电子干 扰信号。在如此恶劣的电磁环境下,准确评估通 信设备的抗干扰能力尤为重要。

通信干扰 信 号 模 拟 设 备[2]用 于 构 建 贴 近 实 战、逼真的干扰环境,可在实验室条件下模拟对通 信及导航链路的各种干扰,主要包括指挥通信链 路干扰、遥测遥控链路干扰、弹间数据链干扰和卫 星导航干扰[3-4]等。

本文设计开发了一种软件无线电架构的干扰 信 号 模 拟 设 备,对通信设备的抗干扰性 能进行 测试[5]。

1 系统设计

1.1 设计原则

通信干扰信号模拟设备(以下简称干扰信号 模拟设备)基于 Xilinx公司的高性能现场可编程 逻辑门阵列(FPGA)平台实现,具有软件可重构、 功能可升级的特点,以满足模拟新类型通信干扰 信号的需求。设计原则如下:

a)针对性 原 则:根 据 飞 行 器 机 动 性 强、多 链 并存、电磁环境复杂等特点,有针对性地进行系统 设计;

b)逼 真 性 原 则:逼 真 模 拟 战 场 威 胁 干 扰 信 号,包括电子对抗部队及电子战飞机的通信干扰 信号、背景信号等;

c)对抗性原则:模拟实现电子战的电磁攻防 过程,满足抗干扰性能测试的试验条件要求;

d)可控性原则:构建的干扰信号可根据不同 的试验内容和参试装备进行控制调整;

e)标准化、可 扩 展 原 则:充 分 利 用 软 件 无 线 电技术和可重构理念,采用标准化、模块化设计。

1.2 系统组成及工作流程

干扰信号模拟设备由电源模块、控制模块、干 扰信号产生模块、上变频通道模块、本振与标频模 块、母板等组成,如图1所示。采用基于标准总线的 模 块 化 硬 件 单 元,具有较强的灵活性和可扩 展性。

图1 干扰信号模拟设备组成框图

其中,电源模块负责整个设备的电源供电;控 制模块负责对外接口和对内控制,包括接收遥控 指令、下发干扰指令、控制干扰信号产生模块完成 信号产生、切换设备工作模式等;干扰信号产生模 块负责实时产生所需要的干扰样式;本振和标频 模块负责产生射频本振信号和参考时钟信号;上 变频通道模块负责将基带信号上变频到指定的频 率;最终产生干扰信号由射频输出端口送出。

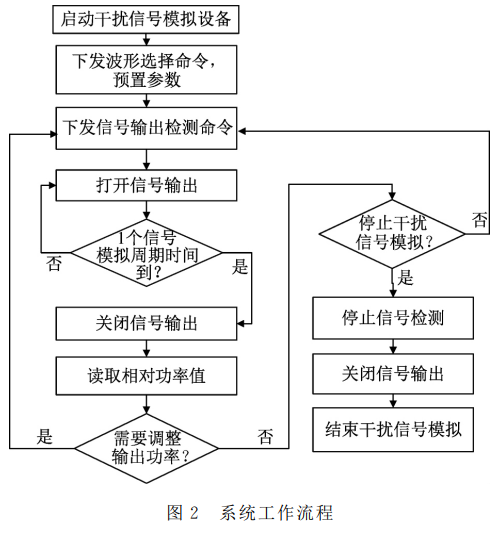

系统工作流程如图2所示。启动干扰信号模 拟设备,下发波形选择命令并预置参数,打开干扰 模拟信号输出,即可进行测试。如需进行干扰功 率调整,先关闭信号输出,测量信号相对功率值, 调整信号功率后,再输出信号进行测试。

3 干扰信号产生模块

干扰信号产生模块根据控制模块传递的干扰 样式参数,相应地产生各种通信干扰信号。

3.1 干扰信号产生模块组成

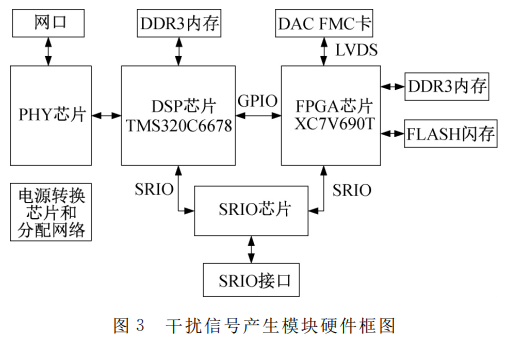

模块硬件组成如图3所示,包括内置 高 速 数 模转 换(DigitaltoAnalogueConversion,DAC) 芯片 的 FPGA 夹 层 卡 (FPGA MezzanineCard, FMC)、高速大容量 FPGA 芯片、高性能数字信号 处理器(DigitalSignalProcessor,DSP)芯 片、高 速串 行 传 输 接 口 (SerialRapidInput Output, SRIO)芯片、DDR3内存芯片、FLASH 闪存芯片、 以太网物理 层(PhysicalLayer,PHY)接 口 芯 片 和电源转换 芯 片 等。DSP 芯 片 和 FPGA 芯 片 之 间采 用 了 通 用 输 入 输 出 接 口 (GeneralPurpose InputOutput,GPIO),具有通 用 可 编 程,使 用 方 便的特点。FPGA 芯片和数模转换 FMC 卡之间 采用了 低 压 差 分 信 号 (Low-VoltageDifferential Signaling,LVDS)进行传输,具有低误码率、低串 扰等优点,适合高速数字信号传输。模块软件具 有动态可重构特性,可实现信号样式的动态配置, 以及功能的快速修改和升级。

模块的核心硬件为任意波形产生单 元,核 心 软件为干扰样式生成软件。干扰样式生成软件在 FPGA 平台上实现。

3.2 任意波形产生单元

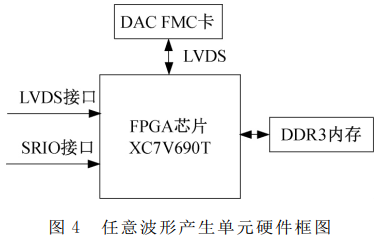

任意波形产生单元是干扰信号产生模块的主 要功能实现单元。通过设置每个干扰信号的调制样式、载频、信号幅度等参数,并依据一定规则控 制每个信号的出现与隐没,实现干扰波形的产生。 单元硬件框图如图4所示。

单元由 XilinxV7系 列 的 FPGA 芯 片、大 容 量 DDR3内 存 芯 片 及 带 有 高 性 能 DAC 的 FMC 卡共同组成。任意波形产生单元一方面负责前端 数据接口控制、存储管理、时钟分配、地址累加、后 端数据差分驱动,另一方面负责调制样式的存储、 输出电平控制、数字正交上变频等一系列功能以 及部分特殊样式信号的产生。

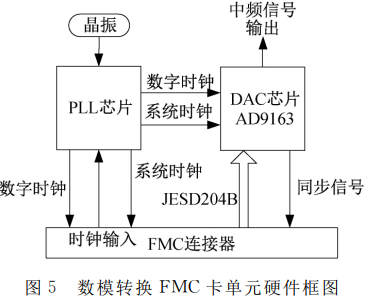

数模转换 FMC 卡 主 要 包 括1片 DAC 芯 片 和1片锁相环(PhaseLockedLoop,PLL)芯片, 单元硬件框图如图5所示。

DAC芯片选用 ADI公司的单通道射频数模 转换芯片 AD9163,具有16bit位宽,支持6Gsps 数 据 率,最 高 12 Gsps 采 样 率。 芯 片 采 用 JESD204B接口协议,还可以支持高达12.5Gbps 数据率,或5Gsps的实数据输入、2.5Gsps的复 数 据 输 入。 芯片的数字通路提供 6 倍、8 倍、 12倍、16倍或24倍内插模式,内含48bit相位精 度的数 控 振 荡 器(NumericallyControlledOscil- lator,NCO)。

3.3 干扰样式生成软件

干扰样式 生 成 软 件 用 于 产 生 窄 带 的 单 音 干扰、噪声调频干扰和宽带的梳状谱拦阻干扰、扫频 干扰等多种干扰样式。主要干扰样式如下:

a)单 音 干 扰:即 单 频 正 弦 波 信 号,直 接 由 FPGA内部 NCO 产生;

b)调制干扰:采用通信调制波形,包括频移 键控(FrequencyShiftKeying,FSK)、二 进 制 相 移键 控(BinaryPhaseShiftKeying,BPSK)、正 交 相 移 键 控 (QuadraturePhaseShift Keying, QPSK)等,根据各调制方式对应的公式进行正交 调制处理,得到干扰信号;

c)直扩干 扰:采用直接序列扩频通信波形, 伪码 类 型 为 m 序 列、Gold 序 列 等,可 根 据 多 项 式、初相等参数通过移位寄存器实时产生;

d)噪声调频干扰:采用噪声对载波进行调频 后形成的一种随机噪声信号。由基带噪声信号经 过正交 变 换,得 到I、Q 两 路 的 基 带 信 号,该 信 号 经过内插滤波处理后和 NCO 混频得到频率调制 信号;

e)梳状谱拦阻干扰:时域和频域上同时存在 并相互独立的多个干扰信号,每根干扰谱线的功 率大小和调制样式可变。可通过设置信号数量、 频率集、幅度等参数,由多路独立干扰样式叠加计 算产生;

f)宽带扫频干扰:信号的载频在较宽的频段 内,按照一定的速度、带宽和扫频顺序陆续扫过所 有的频率信号而连续变化所形成的干扰。由 FP- GA 内部的直接数字合成(DirectDigitalSynthe- sis,DDS)功能模块实现。根据扫频速率、驻留时 间、扫频步进等参数生成时变频率控制字,实现宽 带扫频干扰。

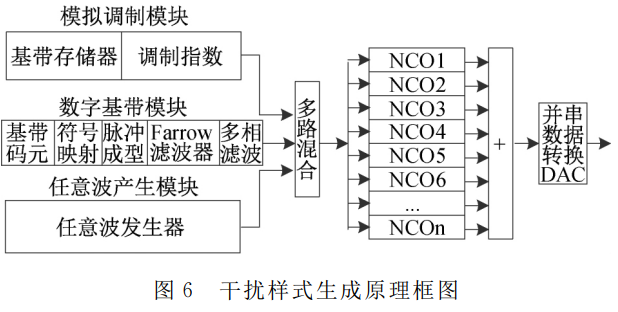

以上干扰 样 式 均 基 于 FPGA 的 软 件 无 线 电 架构实现,详细工作原理如图6所示。

模拟调制模块采用基带波形生成模拟调制信 号,如噪声调频等。

任意波产生模块存储了事先设计好的高采样 率基带波形,可以直接调用。

数字基带模块较为复杂,其中的基带 码 元 产 生单元用来生 成 数 字 调 制 信 号,如 BPSK、QPSK 等调制信号。基带信号按照设定的码速率送入数 字调制器,映射为某种调制方式的I、Q 两路基带 信号。基带I、Q 信 号 经 过 脉 冲 成 型、内 插、滤 波 处理,完成任意倍采样速率转换,得到固定高采样 率(与 DAC 采 样 频 率 匹 配)的 基 带 信 号,其 中 的 任意倍采 样 速 率 转 换 滤 波 器 采 用 Farrow 结 构。 该信号再经过多相滤波,得到等效采样率更高的 基带信号。

为了与多相基带信号匹配,NCO 产生的载波 信号也是多相、多路输 出 的,因 此 需 要 多 个 NCO 同时工 作。这 样,高采样率的基带信号 与 NCO 混频,可得到独立调制的单目标干扰信号。多相 基带信号与 NCO 混频后的信号经过加法器合成 独立调制的多目标干扰信号。

4 测试结果

本文中实现的干扰信号 模拟设备以 Xilinx V7系列 的 FPGA 芯 片 为 处 理 核 心,软 件 综 合 后 的逻辑资源使用率为:触发器30%、查找表35%、 乘法器40%,说明该 FPGA 完全能够满足本文的 设计需要,并为后续升级留有资源空间。

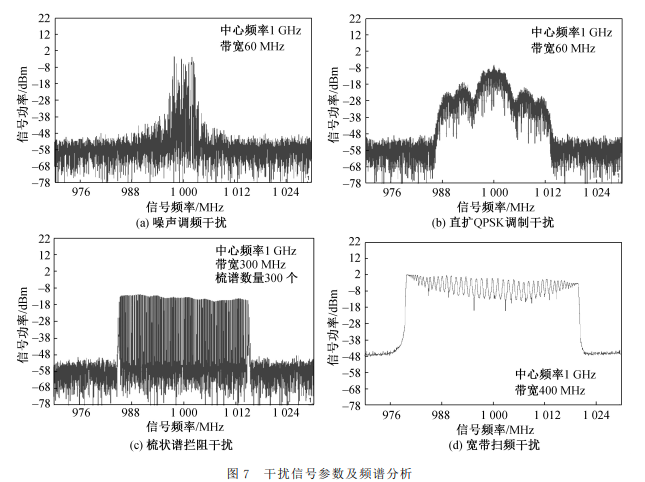

系统测试时,按照流程分别模拟了噪声调频 干扰信号、直 扩 QPSK 调 制 干 扰 信 号、梳 状 谱 拦 阻干扰信号及宽带扫频干扰信号,并采用安捷伦 公司的频谱分析仪进行观察和分析。干扰信号参 数及频谱分析结果如图7所示。

从图7频谱分析结果可以看出,设备 生 成 的 干扰信号在频率、带宽和波形上均符合设计要求。 不足之处包括:(1)QPSK 调制干扰的边带抑制性 能较差;(2)梳状谱拦阻干扰和宽带扫频干扰的带 宽内不同频率存在幅度不一致的现象。以上不足 可以通过系统的软硬件优化进行改善。

5 结论

本文设计了一种软件无线电架构的干扰信号 模拟设备,可在实验室环境下模拟对通信及导航链路的各种干扰,包括噪声调频干扰、调制干扰、 梳状谱拦阻干扰和宽带扫频干扰等。测试结果表 明:干扰频率、带宽、波形特性等各项技术指示符 合要求,满足通信设备抗干扰性能测试需求。

参考文献

[1] 李艳斌.通信电子战面临的挑 战[J].无 线 电 通 信 技术,2013,39(2):1-3.

[2] 于胜 云,左 佑,高 希 光.多通道数字干扰源设计 与 实现[J].舰船电子对抗,2017,40(4):20-22,36.

[3] 孔瑛.现代战争中的电子干扰和反干扰技术[J]. 火控雷达技术,2006,35(4):93-96.

[4] 宁国强,张卫东,侯 波,等.通 信 中 干 扰 及 抗 干 扰 技 术综述[J].四川兵工学报,2011,32(5):115-119.

[5] 周朋.通信对抗干扰效果评估方法综述[J].通 信 技术,2006,49(8):102-103

售前咨询专员

售前咨询专员