技术分享

了解最新公司动态及行业资讯

基于软件无线电的 ADS-B接收机设计与实现

周新发,张开锋 (解放军75841部队,海口,570236)

摘 要:ADS-B接收机在商用航空领域得到了越来越广泛的应用。传统 ADS-B接收机通常基于 PC系统或 ASIC平台。针对传统 ADS-B接收机实时性和灵活性难以兼顾的问题,文章设计实现了基 于软件无线电的 ADS-B接收机。文章首先对 ADS-B接收机的关键技术进行分析,提出了基于软件无 线电的设计思路,并以此为依据设计 ADS-B接收机。文章对该接收机的组成与功能、性能与特点进行 了详细的介绍说明,最后给出系统性能测试结果。

关键词:广播式自动相关监视;软件无线电;FPGA

0 引 言

商用航空器利用广播式自动相关监视(ADS-B) 发射机向外部空间周期性地以广播形式发送飞行器 的ID号、经纬度、气压高度、运行速度和其他一些参 数信息[1]。ADS-B地面站设备或安装了 ADS-B数据 报文接收设备的其他飞行目标接收此 ADS-B数据报 文,通过对报文的解析,获取此飞行目标的位置和飞 行状态数据信息,从而实现对飞行目标的监视[2]。

传统的 ADS-B 接收机通常基于 PC 系统[3]或 ASIC平台,其实时性和灵活性难以兼顾。软件无 线电和SoCFPGA 技术的发展为实现嵌入式 ADS- B实 时 接 收 机 成 为 可 能。文 章 提 出 了 一 种 基 于 AD9363 和 Xilinx Zynq-7000 All Programmable SoC软件无线电平台的 ADS-B接收机实现方案,采 用 AD9363实现射频接收,FPGA 完成 ADS-B信号 的实时解码,并通过 ARM 实现千兆网通信,实现了 灵活性和实时性的统一。

1 ADS-B接收机关键技术分析

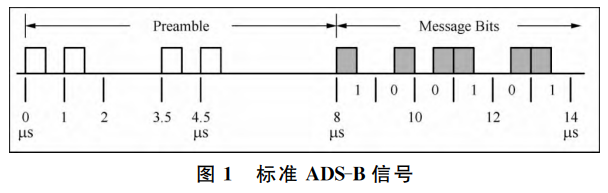

国际民用航空组织S模式超长电文规范定义了 飞行数据格式,其 ADS-B信号如图1所示。

ADS-B的S模式波形相当简单,但要成功接收

并解码消息,仍有若干挑战需要解决。

(1)接收环境通常是长时间空闲中穿插着非常 短的消息;如果发射信号的航空器距离接收机很远, 收到的信号可能非常弱。接收机需要利用前同步码 在拥堵的频段中识别高和低两个幅度的S模式传输。

(2)在1μs位间隔内,各位的可能模式有两种。 位判定的依据是基于时间的模式,因此,接收机需要 利用前同步码准确找出消息位开始的I/Q 样本。

(3)S模式消息由88个信息位和24个校验和 位组成。接收机需要能够在正确的时间清除寄存 器、做出位判定、计算校验和并读取校验和寄存器。 为使接收机正确工作,必须对时序进行精确控制。

(4)对于嵌入式设计,解码过程必须逐个样本 进行。存储大量数据再进行批处理的接收机设计, 对嵌入式系统来说是不现实的。

根据对 ADS-B信号的特点进行分析,实现嵌入

式 ADS-B实时接收机需要解决以下几项关键技术。

1)微弱射频信号采集技术

由于 ADS-B信号的突发性和飞机飞行高度可 能经常发生变化,给 ADS-B信号的稳定接收带来了 较大的挑战。为此,我们采用全向高增益天线+低 噪声放大器实现 ADS-B信号接收,并采用单片 RF 收发器 AD9363完成射频信号采集。

2)ADS-B实时解码技术

ADS-B信号由 112或 56个信息脉冲构成,解 码时对实时性的要求非常严格[4,5]。为了达到实时 解码 的 目 的,采 用 FPGA 逻 辑 实 现 信 号 解 码。FPGA的高速并行处理能力,可以为 ADS-B信号实 时解码提供可靠保证。

针对 ADS-B接收机的技术特点,文章采用基于 SoCFPGA 的软件无线电系统设计技 术。在 完 成 ADS-B信号解码后,还需要将解码结果通过网口上 报到监控系统。SoCFPGA 内部集成大容量可编程 逻辑和高性能 ARM 处理器,并可通过片内 AXI总 线实现数据交互。通过 ARM 的高效低功耗的数据 处理能力和 FPGA 的高速并行处理能力,可以更有 效地为报头检测和数据预处理提供可靠的依据。另 外,ARM 处理器自带 USB 和以太网等多种外设, 可以很方便地实现与监控系统的数据通信。

2 ADS-B接收机系统设计与实现

2.1 硬件设计

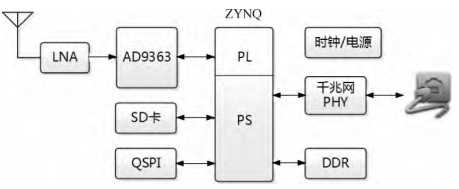

ADS-B接收机由接收天线、LNA、AD9363、FP- GA 最小系统以及时钟电源等组成。ADS-B接收机 硬件系统框图如图2所示。

图2 ADS-B接收机硬件系统框图

ADS-B信号经接收天线进入到 LNA,经 LNA 放大后,输入到 AD9363。AD9363将 ADS-B 信号 转换成基带信号,输出给 FPGA 进行解调。FPGA 的 PL 端,通 过 可 编 程 逻 辑 实 现 ADS-B 报 文 的 解 析。FPGA 的 PS端包括一个双核 ARM 处理器,运 行 LINUX操作系统,将解析完成的 ADS-B信息通 过千兆网输出给上位机进行进一步显示分析。

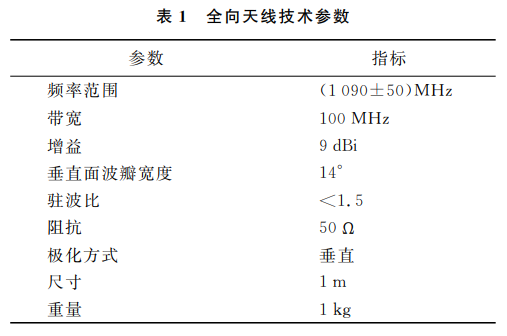

1)天线设计

由于 ADS-B 信 号 可 能 来自不同的方向,且天线的 接收性能直接决定系统性能 的优 劣,因 此,ADS-B 接 收 机选 用 高 增 益 全 向 接 收 天 线。全向天线如图3所示。

全向天线技术参数如表 1所示。

2)AD9363简介

AD9363是 ADI公司推出的集成式可编程 RF收 发器,其高线性度和噪声性能降低了对外部元件的 要求。另外,AD9363的高度集成简化了系统开发, 减少了元件数量,降低了 BOM 成本,同时实现了更 小的尺寸和更高的电源效率。其技术特性如下:

(1)双通道发射器(TX):4路差分输出;

(2)双通道接收器(RX):6路差分或12路单端输入;

(3)可调谐范围:325MHz至3800MHz;

(4)可调谐带宽:200kHz至20MHz;

(5)支持频分双工(FDD)和时分双工(TDD)工 作模式;

(6)出色的接收器灵敏度,噪声系数小于3dB;

(7)接收器增益控制;

(8)CMOS/LVDS数字接口。

从AD9363的技术特性可知,其覆盖了ADS-B的 1090MHz频段,且通过 LVDS数字接口可与 FPGA 方便地进行数据通信,能够满足系统的设计要求。

3)Zynq最小系统设计

Zynq-7000可扩展处理平台是采用 Xilinx新一 代 FPGA(Artix-7与 Kintex-7FPGA)所采用的同 一28nm 可编程技术的最新产品系列。可编程逻辑 可由用户配置,并通过“互连”模块连接在一起,这样 可以提供用户自定义的任意逻辑功能,从而扩展处 理系统 的 性 能 及 功 能。Zynq-7000SoC 系 列 集 成 ARM 处理器的软件可编程性与 FPGA 的硬件可编 程性,不仅可实现硬件加速,同时还在单个器件上高 度 集 成 CPU、DSP、ASSP 以 及 混 合 信 号 功 能。 Zynq-7000的 PS端具有以下技术特性:

(1)集成 ARM CORTEXA9处理器;

(2)集成16、32位 DDR控制器;

(3)集成两个10/100/1000M 以太网 MAC控制器;

(4)集成两个 USB2.0控制器;

(5)集成两个 CAN2.0控制器;

(6)集成两个SD/SDIO2.0/MMC3.31控制器;

(7)集成两个SPI控制器;

(8)集成两个 UART 控制器。

根据 ADS-B接收机的系统需求,Zynq最小系 统挂接一片512G DDR 用于运行 LINUX 系统,挂 接 QSPI和 SD 卡用于存储固件,挂接一片 MAR- VELL公司的千兆网 PHY 芯片88E1513实现一路 千兆网接口,用于与上位机实现数据通信。另外,还 设计了一路 UART,用于系统调试。

2.2 逻辑及软件设计

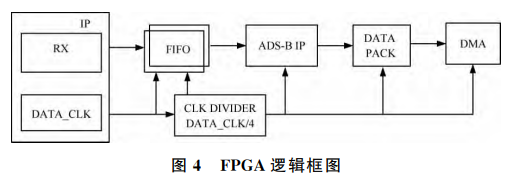

1)逻辑设计

全向天线接收到的 ADS-B信号经低噪放大器放 大后,送到 AD9363进行射频信号采集。ARM 通过 AXI总 线 控 制 AD9363IP 核 配 置 AD9363 以 接 收 ADS-B信号,并将读取到的 ADS-B信号送到 FPGA 逻辑部分进行解码。AD9363IP内核实现了 AD9363 收发器芯片与Zynq器件之间的LVDS接收和发送数 据接口,以及与设计其余部分的数据接口。DMA 模 块用于 AD9363IP与 DDR存储器之间的高速数据传 输。AD9363IP模块的数据接口包括4条用于接收 的数据线和4条用于发送的数据线,对应于 AD9363 的两个接收通道和两个发送通道的I/Q 数据。每条 数据线都是16位宽。为使系统内部的数据传输效率 更高,接收和发送数据被包装到由 DMA 模块管理的 64位宽总线中。AD9361IP的16位并行数据线通过 打包和解包模块连接到 DMA。

ADS-BIP在数据中检测有效 ADS-B帧,ADS-B 帧通过 DMA模块传输到系统的 DDR存储器。ARM 读取 ADS-B帧,进行解码操作。解码结果通过网口 上报到监控系统。FPGA逻辑框图如图4所示。

2)软件设计

软件包括 ARM 软件和上位机软件两部分。 ARM 软件主要实现以下几个功能:

(1)配置 AD9363以接收 ADS-B信号;

(2)从 ADS-BIP内核读取数据;

(3)在读取的数据中检测有效 ADS-B帧;

(4)解码并显示 ADS-B信息;

(5)将解码后的 ADS-B 信息通过千兆网发送 到上位机。

使用 ADI提 供 的 Libiio 库 可 以 方 便 地 配 置 AD9363以及接收和发送数据。逻辑端 ADS-BIP 的输出数据通过 DMA 模块传输到系统的 DDR 存 储器。Libiio库将从 ADS-BIP获取的数据放置到 指定大小的存储缓冲器中;等待缓冲器填满;通过指 针访问该缓冲器。一旦缓冲器填满,ADS-B解码算 法便可处理数据。ADS-BIP内核有两个输出通道: 一个通道对应于 ADS-B位流;另一个通道指示一个 有效数据帧在位流中的何处结束。两个通道均包含 相同的数据速率,彼此同步。有效通道中一个等于1 的样本表示数据通道中一个有效帧的最后一位。通 过解析这两个通道,软件可以从位流中提取有效的 ADS-B数据帧,并将数据传送到解码函数。解码函数 解析出 ADS-B信息,并通过千兆网发送到上位机。

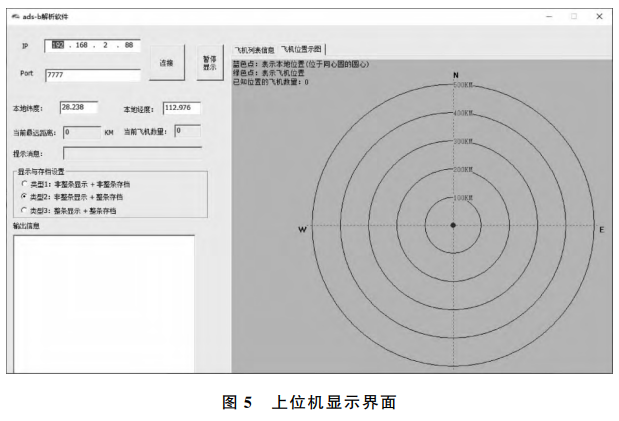

上位机软件根据 ADS-B信息,将飞机的位置、 速度、ID号等进行实时显示,其界面如图5所示。

2.2 系统性能测试

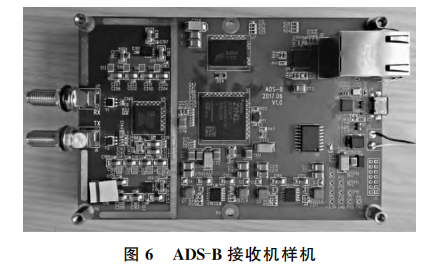

ADS-B接收机样机图片如图6所示。

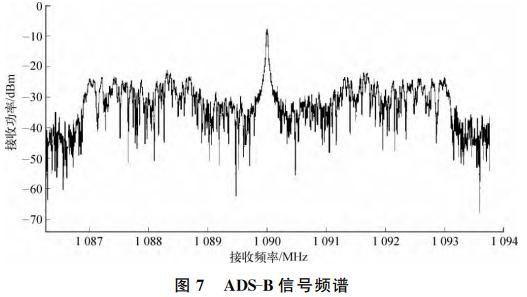

在调试过程中,ADS-B接收机中运行 LINUX,将 采集到的数据发送到PC,通过 PC端的 MATLAB 可 以实时显示 ADS-B的信号频谱,如图7所示。

对 ADS-B接收机的性能进行测试,接收机性能 指标如下:

(1)接收频率范围:(1090±1)MHz;

(2)ADS-B数据发送延迟:小于70ms;

(3)ADS-B数据接收和处理量:400份报/s;

(4)接收灵敏度:-90dBm;

(5)动态范围:大于65dB;

(6)接收距离:不小于450km; (7)功耗:不大于5W;

(8)工作温度:-40~85度。

从测试结果可知,文章设计的基于软件无线电 的 ADS-B接收机具有较高的接收性能和处理性能, 实现了实时性和灵活性的统一。

3 结束语

文章分析了 ADS-B接收机的关键技术,采用基 于软件无线电的设计思路,设计实现了一套 ADS-B 接收机系统。相对于以往的设计,本系统的体系结 构具有结构灵活、实时性强等特点,具有较高的应用 价值。另外,该系统 不 局 限 于 ADS-B 信 号 接 收 功 能,在不修改硬件平台的前提下,通过修改 FPGA 可编程逻辑和 ARM 的代码,可以实现各种通信、信 号处理算法,充分体现了软件无线电的优越性。

参 考 文 献

[1]咸儆醒,李航宇,黄立星.ADS-B地面站测试与评估平台的 设计与实现[J].信息化研究,2019(02):71-74.

[2]索国伟,王金锁,郭荣华,等.ADS-B数据报文采集与解析 系 统 的 设 计 与 实 现 [J].电 子 技 术 应 用,2018(09): 104-107.

[3]段煜,海灏.一种 ADS-B地面站自动测试系统的设计与实 现[J].电子世界,2018(14):152-153. [4]Eurocontrol.ED-129,TechnicalspecificationforA1090 MHzextendedsquitterADS-Bgroundstation[S].France: Eurocae,2010. [5]Rtca.DO-260A,Minimumoperationalperformancestand- ards(MOPS)forairborneequipmentforautomaticdepend- entsurveillance-broadcast(ADS-B)andtrafficinformation service-broadcast(TIS-B)[S].Washington:Rtca,2009.

周新发(1963— ),男,高级工程师,主要研究方 向为无线通信及软件无线电技术等。

售前咨询专员

售前咨询专员