技术分享

了解最新公司动态及行业资讯

基于RFSoC 的超宽带数字接收机设计

摘要: 现代雷达越来越向小型化、智能化、多功能化方向发展,宽带数字化相控阵已成为雷达发展的必然趋势。文中介绍了当前的宽带数字接收机架构,中频数字化和射频数字化接收机的基本原理和发展需求。结合当前微电子技术及信号处理器件的发展,直接对射频信号进行处理已成为可能。为实现基于射频数字化的超宽带数字接收机设计,文中给出了一种基于RFSoC 技术的超宽带数字接收机设计。该接收机可实现直接射频采样和宽带任意波形产生,瞬时带宽可支持2 GHz,测试指标满足雷达、电子战应用需求。基于RFSoC 技术的超宽带数字接收机具备多通道、低成本、低功耗的优点,在雷达、电子战设备及综合射频系统中将获得广泛应用。

关键词: RFSoC; 数字接收机; 超宽带; 小型化

Design of Ultra Wideband Digital Receiver Based on RFSoC

SHANG Linfeng* ,LI Pengfei,ZHANG Yuhua

( Nanjing Research Institute of Electronics Technology, Nanjing Jiangsu 210039,China)

Abstract: With the development direction of miniaturization、intelligence and multifunctionality for modern radar,wideband digital phased-array radar has become an inevitable development trend. In this paper,the structures of wideband digital receiver are introduced , the basic principle and development demand of IF-digitize receivers and RF-digitize receivers are also presented. Based on the development of microelectronics and technologies of signal processing,RF direct sampling can be realized. An ultra wideband RF-digitize receiver based on RFSoC is designed and presented. This multi-channel digital receiver can realize 2 GHz instantaneous bandwidth direct RF sampling and wideband arbitrary waveform generation,the test result of which meets the system requirements.The design will be widely used in radar and electronic warfare system because of its low-cost and low power consumption.

key words: RFSoC; digital receiver; ultra wideband; miniaturization

0 引言

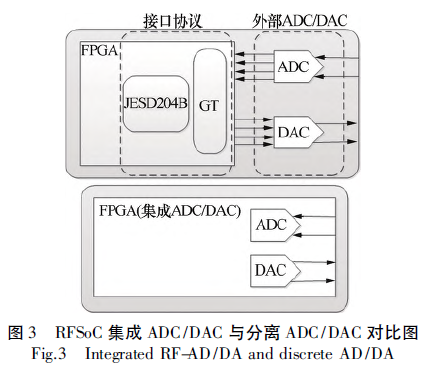

随着军用电子技术的飞速发展,雷达不仅需要具有大空域快速搜索能力、多目标探测跟踪能力、目标识别成像能力,还需具备强生存、协同作战能力,同时实现雷达、电子战、通信等功能,宽带数字化相控阵已成为雷达发展的必然趋势。为适应现代作战平台对雷达、电子战设备的需求,系统对信号带宽的要求越来越高,收发通道的数量越来越多,无线通信系统的适应性和灵活性要求也越来越高,对成本、功耗、小型化等性能指标都在不断提升[1]。基于以上需求,集成了高速模数转换芯片( ADC) 、高速数模转换芯片( DAC) 、可编程逻辑器件( FPGA) 等收发处理一体的RFSoC 芯片应运而生,并且有着自己独特的优势。

RFSoC 中直接集成多路ADC 和DAC,通过IP 核的方式与FPGA 级联,消除了FPGA 与ADC /DAC 的JESD204B /C 接口功耗,系统功耗会随之而大大降低,同时也实现了高集成、小型化设计。基于RFSoC 的直接射频采样相比传统的超外差系统,板级设计简单,RFSoC 可减少或者尽可能减少模拟信号处理器件的数量,提升了平台灵活性,并且可以利用高带宽来优化性能[2]。由于JESD204B 接口的移除,ADC /DAC 延时降低,更便于电子对抗等低延时系统的应用[3]。

基于RFSoC 技术,本文给出了一种新一代超宽带数字接收机设计方案,该设计包含8 路DAC 和8 路ADC。经测试,新设计的基于RFSoC 的超宽带数字接收机各项指标均满足雷达系统使用,另外在低成本、低功耗、小型化方面相对于传统设计具有明显优势,具备极大的工程应用价值。

1 数字接收机架构

1.1 中频数字化

目前数字接收机实现方式主要有中频数字化和射频数字化两种。

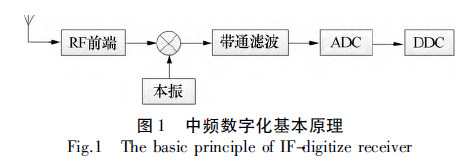

中频数字化,即超外差体制,采用混频的频谱搬移思路,将射频信号转换到中频上,利用ADC 在中频对模拟信号进行数字化,然后采用数字下变频( DDC) 技术,将采样率较低的数字零中频信号送给后续的基带信号处理单元,如图1 所示。

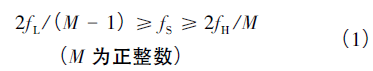

中频数字化的好处是可以降低ADC 的采样率与模拟带宽要求。ADC 的采样率选择遵循带通采样定理。假设模拟带通信号频率限制在( fL,fH) 范围内,采样频率fS满足

则用fS进行等间隔采样所得到的信号采样值可完全代表原带通信号,通过一带通滤波器即可重新恢复原带通信号[4]。

1.2 射频数字化

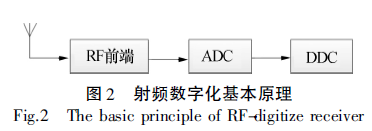

射频数字化采用软件无线电思想,将ADC、DAC尽可能地靠近天线,不通过混频,减少模拟环节,尽早地将接收到的模拟信号数字化,然后用全数字化方式对接收的信息进行处理,如图2 所示。

随着微电子技术及信号处理器件的发展,直接对射频信号进行处理已成为可能。从理论上讲,采用射频采样架构具有更好的可扩展性和更强的适应性,是理想的数字接收机结构。但是这种架构不仅对ADC转换器的性能如转换速率、工作带宽、动态范围等提出了非常高的要求,而且同时对后续数字信号处理器件的处理速度也提出了很高的要求。RFSoC 集成的ADC 具有高采样率、宽模拟带宽、大动态范围,集成的FPGA 资源足够多,可有力支撑射频数字化。

2 基于RFSoC 的宽带接收机设计

本文介绍的基于RFSoC 技术的超宽带数字接收机集成8 通道高速DAC 和8 通道ADC,可实现瞬时带宽2 GHz 的直接射频采样及宽带任意信号产生。该超宽带模块使用16 发16 收的集成光器件,支持10 Gbps光收发,对外可提供任意基带调制码元,对内可用于接收通信编码数据。该设计兼具百兆、千兆、万兆网的对外数据交互能力。该超宽带数字收发平台为标准6U* 5n 模块,尺寸为233.35 mm ×160 mm × 25 mm,所有收发通道最高采样率工作状态下,单板功耗低

于50 W。

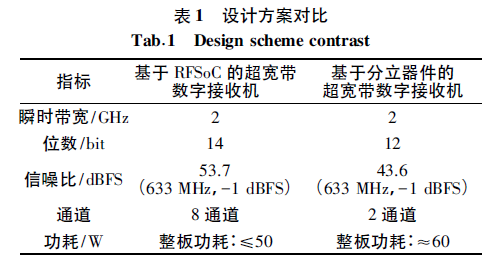

基于RFSoC 技术的超宽带数字接收机相对于传统超宽带数字接收机具有通道更多、成本及功耗更低、指标更好等优势[5]。图3 为二者架构对比。

从表1 可以看出,本文给出的超宽带数字接收机设计满足了当前无线电系统的发展需要,在电子对抗小型化平台、雷达宽带成像及识别、综合射频等领域提供了更加灵活的解决方案。

3 指标测试

3.1 DAC 性能指标测试

RFSoC 内集成了8 路DAC 芯片,从而省去了FPGA中产生的波形数据发送到DAC 芯片过程中所需要的接口协议,不再受限于传统的LVDS 或者JESD204B 接口速率限制,简化了程序设计,同时也提高了信号质量和稳定性。

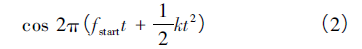

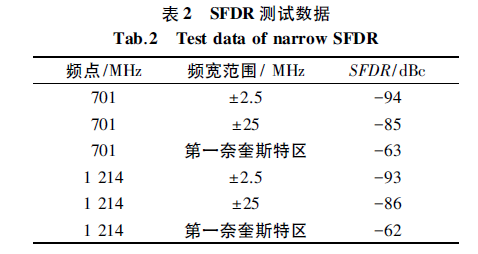

RFSoC 内部IP 提供了16 相数据接口,需要做的只是在FPGA 内部产生输出信号所对应的16 相数据即可。线性调频的实信号数学表达式为

式中: fstart为线性调频的起始频率; k 为调频斜率,即BW/τ,t∈( 0,τ) 。将线性调频信号按抽取率m= 16 并按fs的间隔分别进行抽取,可将其分解为16 相[5]。若采样率为fss,周期为Tss时,从第0 相至第15 相的表达式如下

将式( 2) 中的相位部分展开,将代表频率的项和代表相位的项分别整理得到线性调频信号的频率步进变化关系和相位步进变化关系。根据频率、相位的步进变化关系可计算出每相信号当前时刻的频率控制字和相位控制字,并控制FPGA 中相应的16 路DDS IP核即可产生出想要的多相并行数据[6]。另外,当调制斜率为0 时,让16 相NCO 一直工作,就能产生相应载频的单音信号[7]。

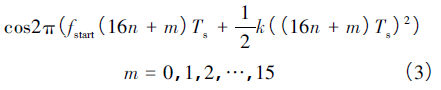

在实验室条件下,对本文介绍的基于RFSoC 超宽带数字接收机进行了测试。根据DAC 的关键指标,首先在参考时钟4.8 GHz 下,测试DAC 的宽带杂散、窄带杂散等指标; 其次、在参考时钟6.4 GHz 下,测试了DAC芯片可输出的的最大瞬时带宽及其带内平坦度。

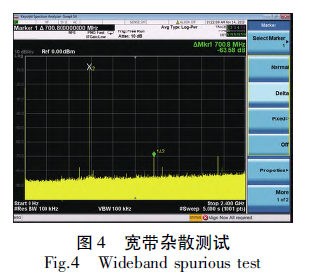

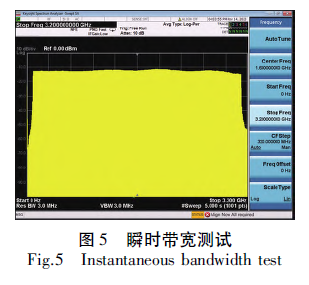

由测试可知,第一区内最大杂散-60 dBc 左右,主要为二次谐波及其组合杂散。表2 为DAC 的杂散测试数据,在± 2 . 5 MHz 内,窄带SFDR优于- 90 dBc ,在±25 MHz 内,窄带SFDR 优于-80 dBc。图4 为输出频点701 MHz 时,整个第一奈奎斯特区最大杂散-63.58 dBc。图5 为瞬时带宽测试,在整个第一奈奎斯特区0 GHz~3.2 GHz 内,输出的信号带宽范围为0.1 GHz~3.1 GHz,3GHz 范围内带内平坦度在2.6 dB 以内。以上指标均高于传统的分立器件设计,原因在于简化数据接口电路,去除了中间链路引入的阻抗失配以及非线性影响。

3.2 ADC 性能指标测试

RFSoC 内集成了8 路ADC 芯片,同样也省去了ADC 芯片采样后的多相数据传递到FPGA 中所需要的接口协议,省掉了接口电路,降低功耗和程序设计难度的同时,也减掉了接口电路上电源纹波以及阻抗不连续对ADC 的性能指标影响。在RFSoC 内部, IP 提供了8 相数据接口,我们将ADC 采样得到的8 相数据通过Vivado 的ILA 界面将数据保存下来,然后通过Matlab 进行16 384 点FFT 数据分析,对ADC 芯片的SNR、SFDR 等关键指标进行测试[8]。

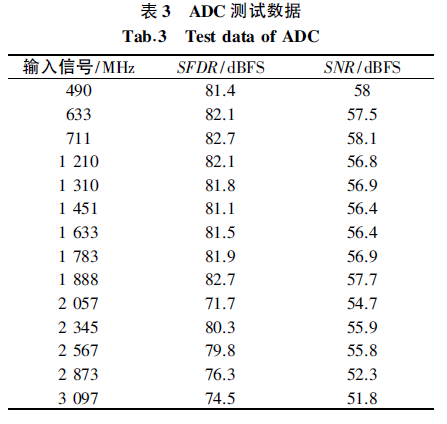

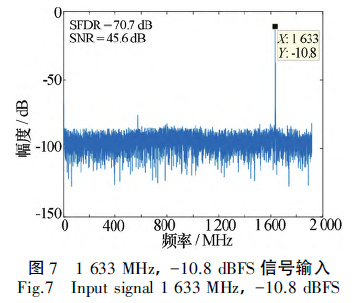

由表3 可以看出,ADC 在-10 dBFS 信号输入时,SFDR 优于70 dBFS,SNR 指标优于50 dBFS。输入信号频率越低,指标越高。当输入信号功率在-10 dBFS时,ADC 的性能测试数据如表3 所示。

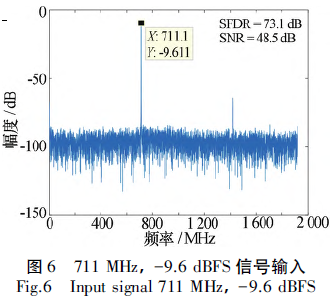

图6 为频率711 MHz,-9.6 dBFS 信号输入,ADC 采样数据Matlab 数据分析图。图7 为频率1 633 MHz ,-10.8 dBFS 信号输入,ADC 采样数据Matlab 数据分析图。由图可看出,在整个第一奈奎斯特区,711 MHz 频率处的SNR 指标为58.1 dBFS。1 633 MHz 频率处的SNR 指标为56.4 dBFS。

4 结束语

在芯片处理系统( SoC) 上单片集成直接射频采样数据转换器,可消除对外部数据转换器的需求,从而可实现一款高度灵活且小型化的超宽带数字接收解决方案[9],与分立器件方案相比,可减少50%的功耗和空间占用,将大部分射频信号处理功能转移至数字域,降低了软硬件设计难度,同时也完成了集成化、单片化的发展趋势需求[10]。在军事需求的强大推动下,配装基于RFSoC 射频系统的小型平台方案受到世界各国的广泛重视,旨在实现产品通信、雷达和电子战模式之间自适应和灵活的切换[11]。本文介绍的基于RFSoC 的超宽带数字接收机设计,各项指标相对于分立器件设计来说均具有明显优势,预计在电子对抗、雷达宽带成像、综合射频等领域将具有极大的应用价值。

参考文献( Reference)

[1] 陈伯孝. 现代雷达系统分析与设计[M]. 西安: 西安电子科技大学出版社,2016.

CHEN Baixiao. Modern radar system analysis and design [M]. Xi'an: Publishing House of Xidian University,2016.

[2] 弋稳. 雷达接收机技术[M]. 北京: 电子工业出版社,2005.

YI Wen. Radar receiver technology[M]. Beijing: Publishing House of Electronics Industry,2005.

[3] 丁鹭飞,耿富录. 雷达原理[M]. 西安: 西安电子科技大学出版社,2000.

DING Lufei,GENG Fulu. Principle of radar[M]. Xi' an:Publishing House of Xidian University,2000.

[4] 吴兵,张飞,伍小保. 宽带数字波形产生中的广义多相滤波[J]. 雷达科学与技术,2016,14( 4) : 422-426.

WU Bing,ZHANG Fei,WU Xiaobao. Generalized multiphase filtering in wideband digital waveform generation[J].Radar Science and Technology,2016,14( 4) : 422-426.

[5] SHRMAN Y D,LESHCHENKO S P,ORLENKO V M. Advantages and problems of wideband radar[C]/ / Proceedings of the 2003 International Radar Conference. Huntsville:IEEE Press,2003: 15-21.

[6] 蒋润良. 基于FPGA 的超宽带波形设计及应用[J]. 现代雷达,2018,40( 4) : 73-76.

JIANG Runliang. Design and application of UWB waveform based on FPGA[J]. Modern Radar,2018,40( 4) : 73-76.

[7] 张宁,谷伟,李彭飞. 基于多相分解的直接宽带雷达信号产生技术[J]. 现代雷达,2020,42( 1) : 82-85.

ZHANG Ning,GU Wei,LI Pengfei. A direct way of generating wideband radar signals based on polyphase decomposition [J]. Modern Radar,2020,42( 1) : 82-85.

[8] 廉昕,姜坤,王元钦,等. 基于并行NCO 的宽带数字下变频器[J]. 电子测量技术,2012,35( 7) : 73-77.

LIAN Xin,JIANG Kun,WANG Yuanqin,et al. Wideband digital down converter based on parallel NCO[J]. Electronic Measurement Technology,2012,35( 7) : 73-77.

[9] 卢胜军,林逸群,范童修,等. 微系统技术及其在电子战接收机中的应用[J]. 微波学报,2016( S2) : 548-552.

LU Shengjun,LIN Yiqun,FAN Tongxiu,et al. Micro system technology and its application in EW receiver[J]. Journal of Microwaves,2016( S2) : 548-552.

[10] CHUANG E,HENSLEY S,WHEELER K. A highly capable arbitrary waveform generator for next generation radar systems[C]/ / 2006 IEEE Aerospace Conference. Big Sky:IEEE Press,2006: 1-7.

[11] 雷正伟,王晓莉,冀鑫炜. 现代雷达系统抗干扰需求分析[J]. 现代雷达,2020,42( 2) : 85-90.

LEI Zhengwei,WANG Xiaoli,JI Xinwei. Analysis on demand of anti-jamming design for modern radar system[J].Modern Radar,2020,42( 2) : 85-90.

作者简介:

商林峰男1986 年生,博士,高级工程师,研究方向为数字接收技术;

李彭飞男1983 年生,硕士,高级工程师,研究方向为数字接收技术;

张玉华男1978 年生,硕士,研究员级高级工程师,研究方向为数字接收技术。

售前咨询专员

售前咨询专员